# **Application Manual** Power Semiconductors

# **Application Manual Power Semiconductors**

Dr.-Ing. Arendt Wintrich

Dr.-Ing. Ulrich Nicolai

Dr. techn. Werner Tursky

Univ.-Prof. Dr.-Ing. Tobias Reimann

Published by

SEMIKRON International GmbH

Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie;

detailed bibliographic data is available on the Internet under http://dnb.d-nb.de

The use of registered names, trade names, trademarks etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

This manual has been developed and drawn up to the best of our knowledge. However, all information and data provided is considered non-binding and shall not create liability for us. Publication of this manual is done without consideration of other patents or printed publications and patent rights of any third party. All component data referred to in this manual is subject to further research and development and, therefore, is to be considered exemplary only. Binding specifications are provided exclusively in the actual product-related datasheets.

The publisher reserves the right not to be responsible for the accuracy, completeness or topicality of any direct or indirect references to or citations from laws, regulations or directives (e.g. DIN, VDI, VDE) in this publication. We recommend obtaining the respectively valid versions of the complete regulations or directives for your own work.

ISBN 978-3-938843-83-3 2nd revised edition

ISLE Verlag 2015 © SEMIKRON International 2015

This manual is protected by copyright. All rights reserved including the right of reprinting, reproduction, distribution, microfilming, storage in data processing equipment and translation in whole or in part in any form.

Published by: ISLE Verlag, a commercial unit of the ISLE Association Werner-von-Siemens-Strasse 16, D-98693 Ilmenau, Germany

Printed by: Gutenberg Druck+Medien GmbH Schleifweg 1b, D-91080 Uttenreuth-Erlangen, Germany

Edited by: SEMIKRON International GmbH Sigmundstrasse 200, D-90431 Nuremberg, Germany

Printed in Germany

# **Preface**

Since the first Application Manual for IGBT and MOSFET power modules was published, these components have found their way into a whole host of new applications, mainly driven by the growing need for the efficient use of fossil fuels, the reduction of environmental impact and the resultant increased use of regenerative sources of energy. General development trends (space requirements, costs, and energy efficiency) and the advancement into new fields of application (e.g. decentralised applications under harsh conditions) bring about new, stricter requirements which devices featuring state-of-the-art power semiconductors have to live up to. For this reason, this manual looks more closely than its predecessor at aspects pertaining to power semiconductor application and also deals with rectifier diodes and thyristors, which were last detailed in a SEMI-KRON manual over 30 years ago.

This manual is aimed primarily at users and is intended to consolidate experience which up till now has been contained in numerous separate articles and papers. For reasons of clarity and where deemed necessary, theoretical background is gone into briefly in order to provide a better understanding of the subject matter. A deeper theoretical insight is provided in various highly-recommendable textbooks, some of which have been cited in the bibliography to this manual.

SEMIKRON's wealth of experience and expertise has gone into this advanced application manual which deals with power modules based on IGBT, MOSFET and adapted diodes, as well as rectifier diodes and thyristors in module or discrete component form from the point of view of the user. Taking the properties of these components as a basis, the manual provides tips on how to use and interpret data sheets, as well as application notes on areas such as cooling, power layout, driver technology, protection, parallel and series connection, and the use of transistor modules in soft switching applications.

This manual includes contributions from the 1998 "Application Manual for IGBT and MOSFET Power Modules" written by Prof. Dr.-Ing. Josef Lutz and Prof. Dr.-Ing. habil. Jürgen Petzoldt, whose authorship is not specifically cited in the text here. The same applies to excerpts taken from the SEMIKRON Power Semiconductor Manual by Dr.-Ing. Hans-Peter Hempel. We would like to thank everyone for granting their consent to use the relevant excerpts.

We would also like to take this opportunity to express our gratitude to Rainer Weiß and Dr. Uwe Scheuermann for their expertise and selfless help and support. Thanks also go to Dr.-Ing. Thomas Stockmeier, Peter Beckedahl and Thomas Grasshoff for proofing and editing the texts, and Elke Schöne and Gerlinde Stark for their editorial assistance.

We very much hope that the readers of this manual find it useful and informative. Your feedback and criticism is always welcome. If this manual facilitates component selection and design-in tasks on your part, our expectations will have been met.

Nuremberg, Dresden, Ilmenau; November 2010

Arendt Wintrich Ulrich Nicolai Tobias Reimann Werner Tursky

# Contents

| 1 |            | iconductors: Basic Operating Principles                             |    |

|---|------------|---------------------------------------------------------------------|----|

|   | 1.1 Basics | for the operation of power semiconductors                           | 1  |

|   | 1.2 Power  | electronic switches                                                 | 5  |

| 2 | Rasics     |                                                                     | 13 |

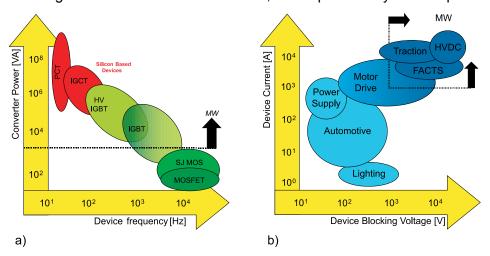

| _ |            | tion fields and current performance limits for power semiconductors |    |

|   |            | ctifiers                                                            |    |

|   |            | ctifier diodes                                                      |    |

|   |            | General terms                                                       |    |

|   |            | Structure and functional principle                                  |    |

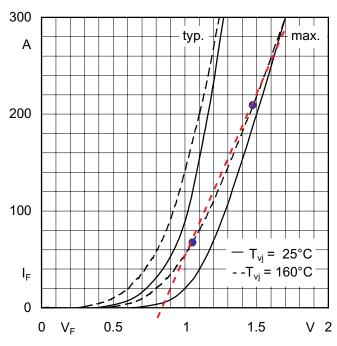

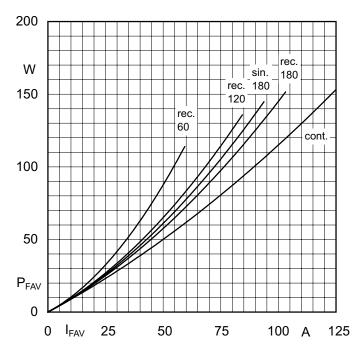

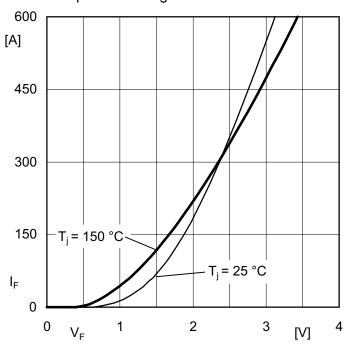

|   |            | Static behaviour                                                    |    |

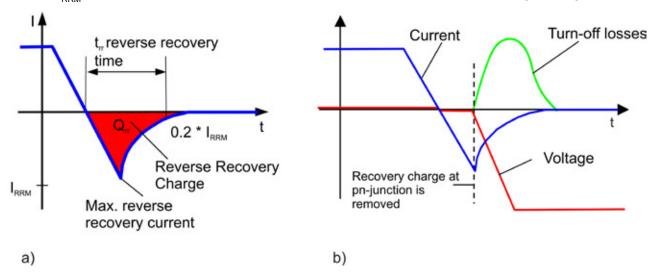

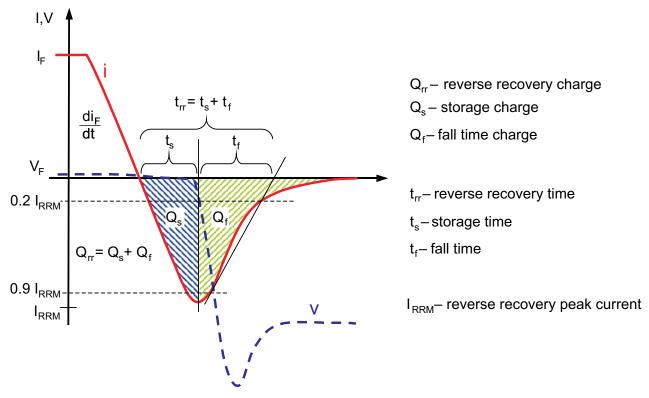

|   |            | Dynamic behaviour                                                   |    |

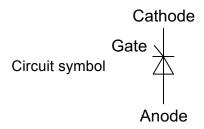

|   |            | yristors                                                            |    |

|   |            | General terms                                                       |    |

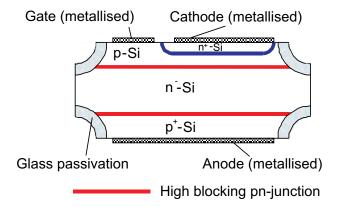

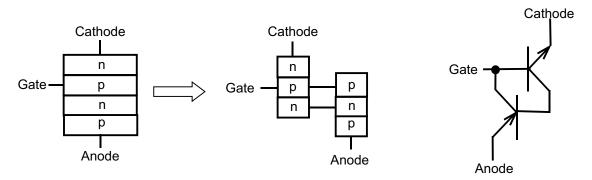

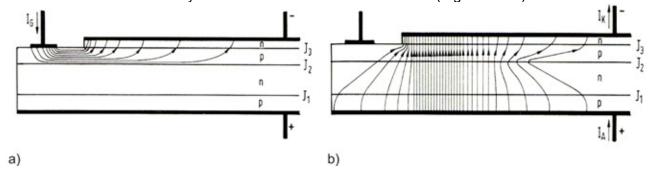

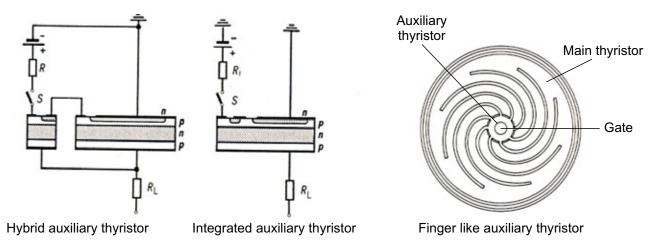

|   |            | Structure and functional principle                                  |    |

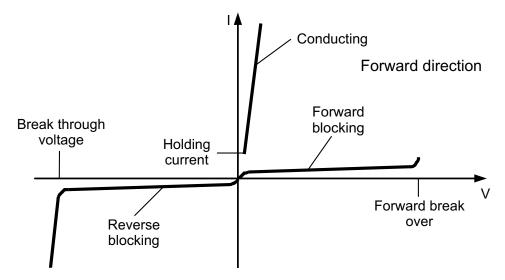

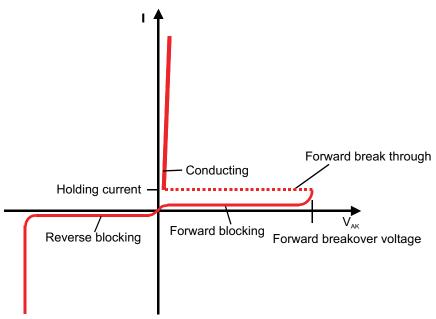

|   |            | Static behaviour                                                    |    |

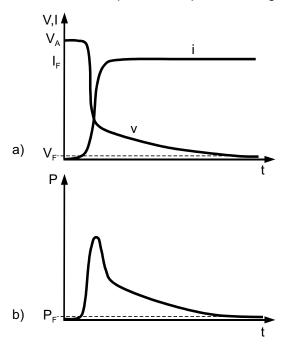

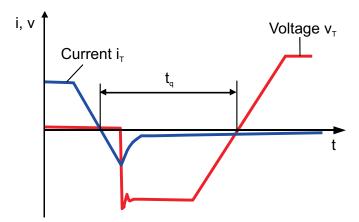

|   |            | Dynamic behaviour                                                   |    |

|   |            | eeling and snubber diodes                                           |    |

|   |            | ucture and functional principle                                     |    |

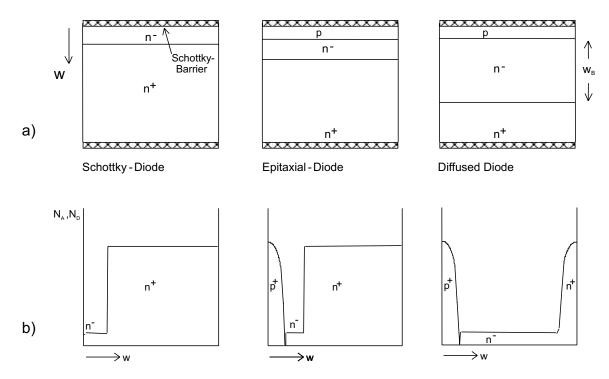

|   |            | Schottky diodes                                                     |    |

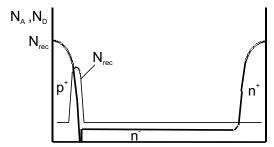

|   |            | PIN diodes                                                          |    |

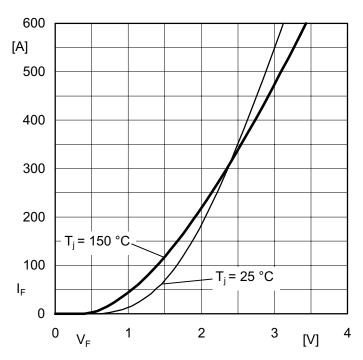

|   |            | atic behaviour                                                      |    |

|   |            | On-state behaviour                                                  |    |

|   |            | Blocking behaviour                                                  |    |

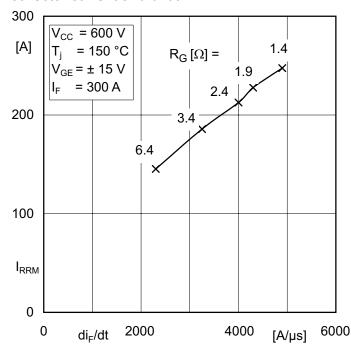

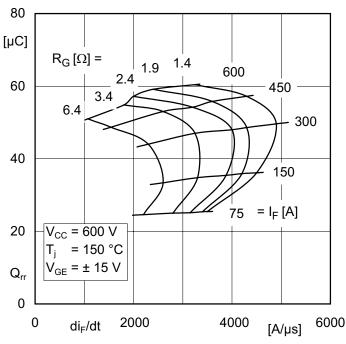

|   |            | namic behaviour                                                     |    |

|   | •          | Turn-on behaviour                                                   |    |

|   |            | Turn-off behaviour                                                  |    |

|   |            | Dynamic ruggedness                                                  |    |

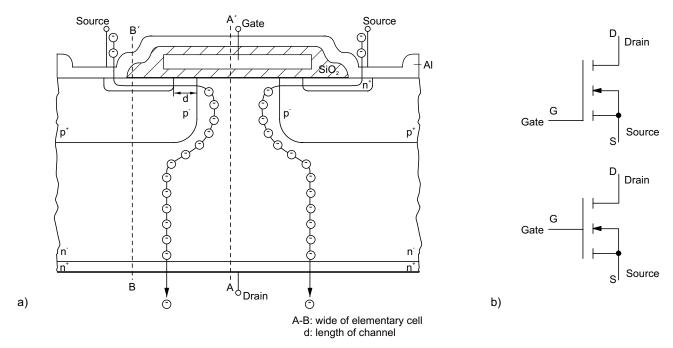

|   | 2.4 Power  | MOSFET and IGBT                                                     | 43 |

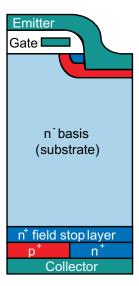

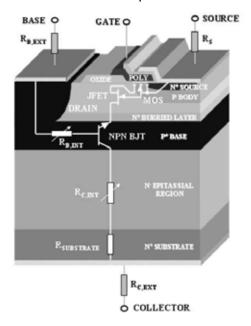

|   |            | ucture and functional principle                                     |    |

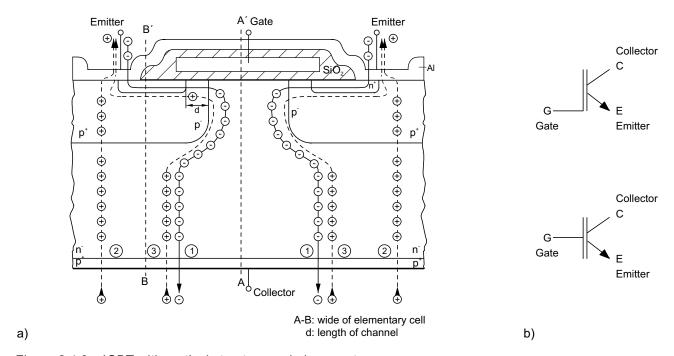

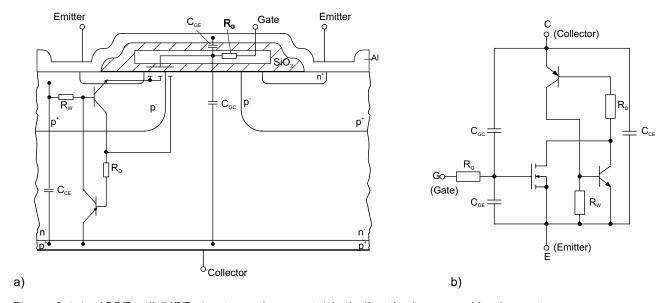

|   | 2.4.2 IGI  | BT                                                                  | 46 |

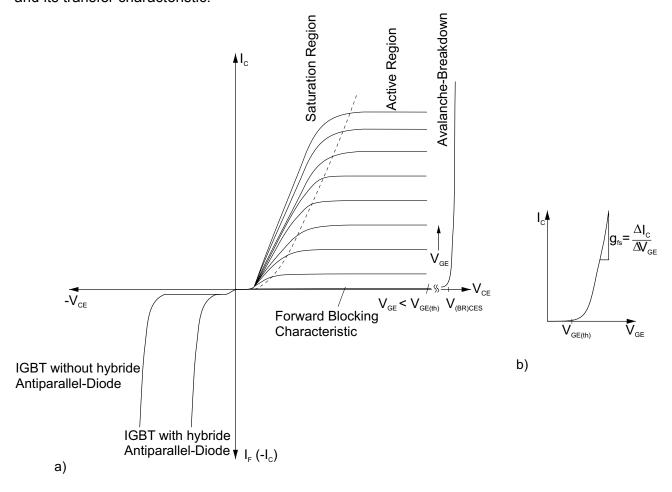

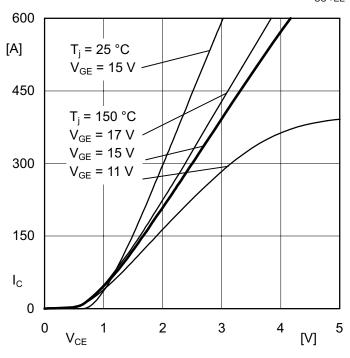

|   |            | Static behaviour                                                    |    |

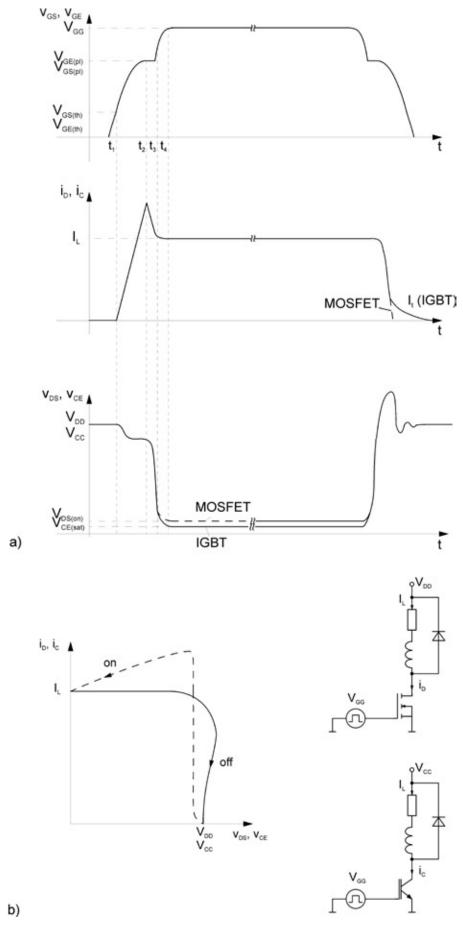

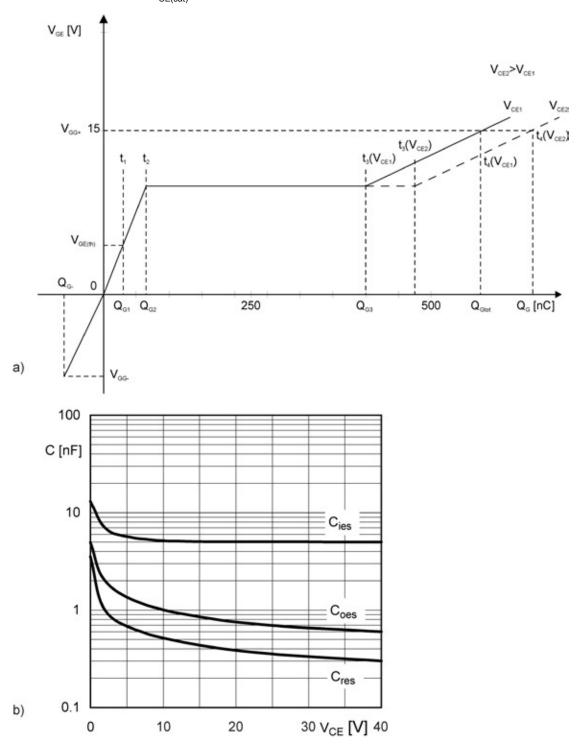

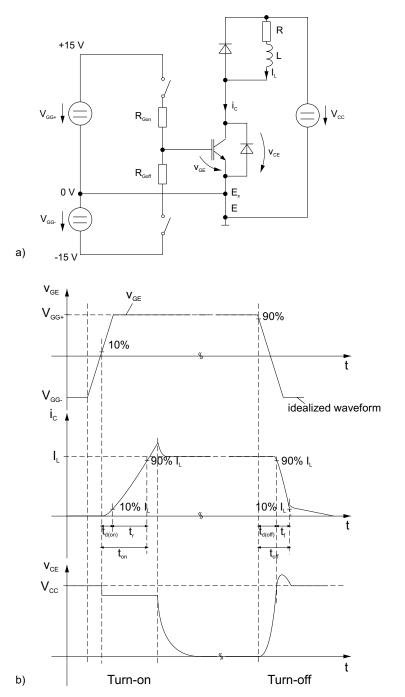

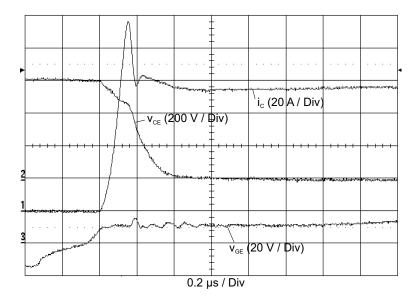

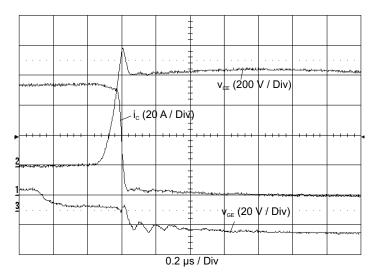

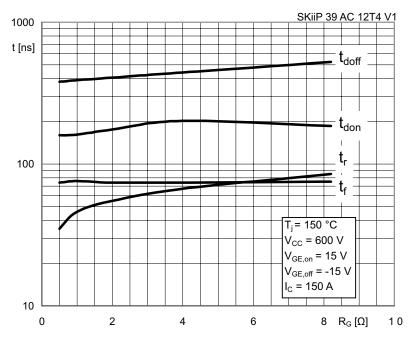

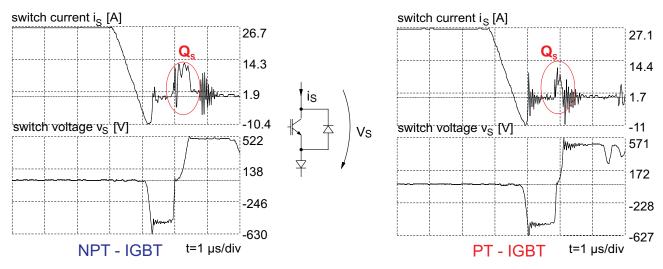

|   |            | Switching behaviour                                                 |    |

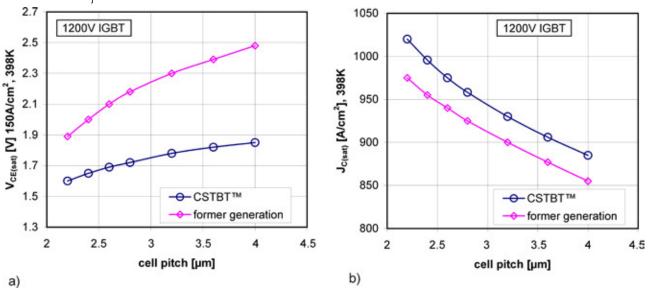

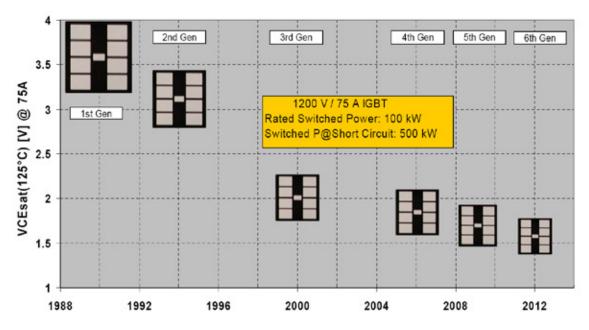

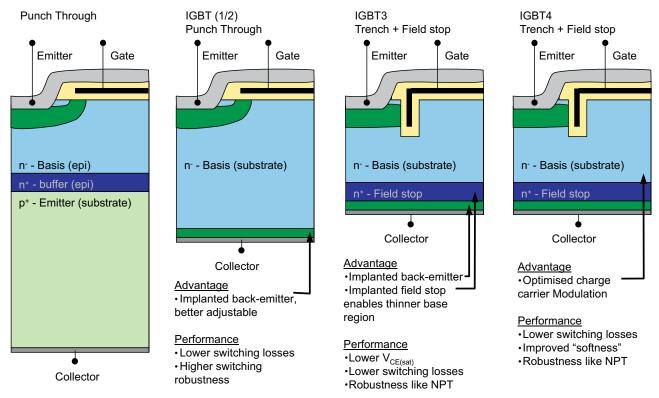

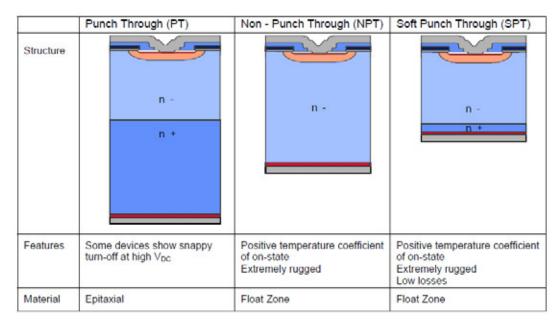

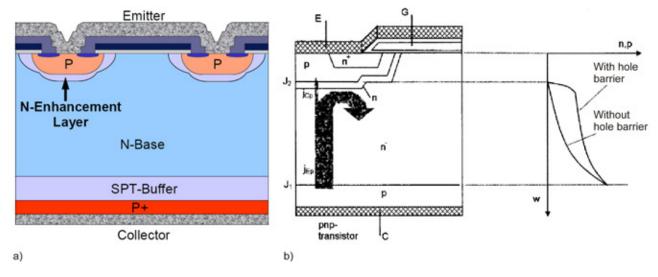

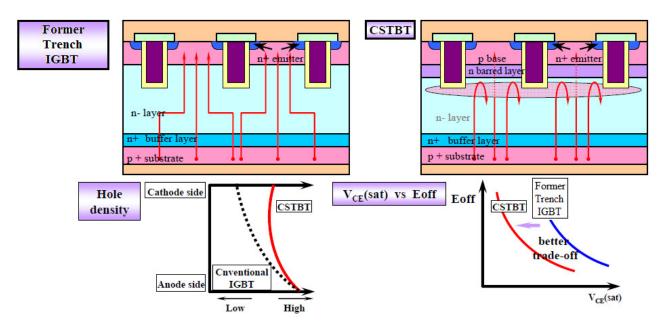

|   |            | IGBT – Concepts and new directions of development                   |    |

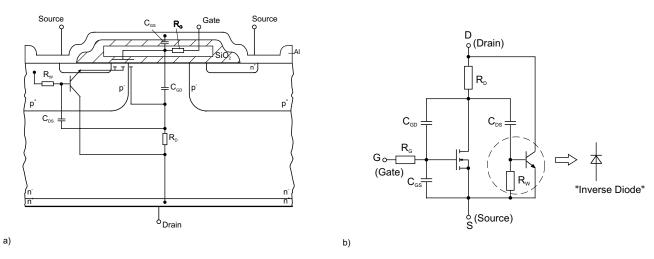

|   |            | wer MOSFET                                                          |    |

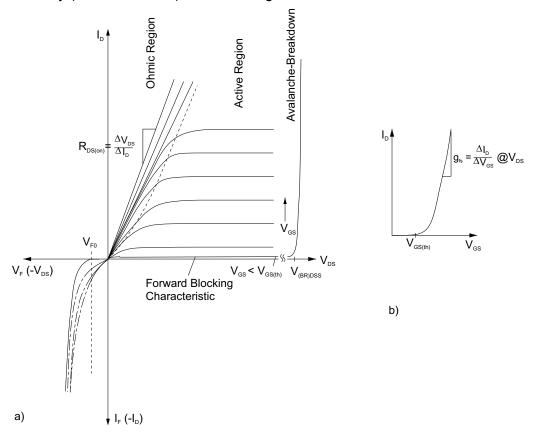

|   |            | Static behaviour                                                    |    |

|   |            | Switching behaviour                                                 |    |

|   |            | Latest versions and new directions of development                   |    |

|   |            | ing                                                                 |    |

|   | -          | chnologies                                                          |    |

|   |            | Soldering                                                           |    |

|   |            | Diffusion sintering (low-temperature joining technology)            |    |

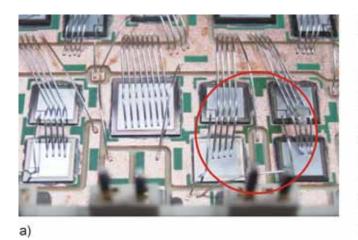

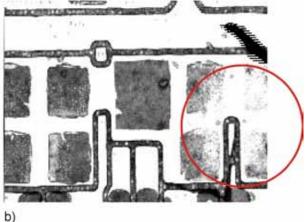

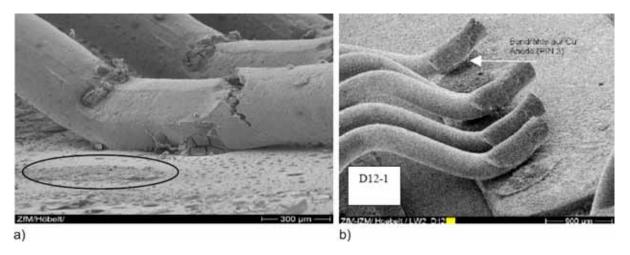

|   |            | Wire bonding                                                        |    |

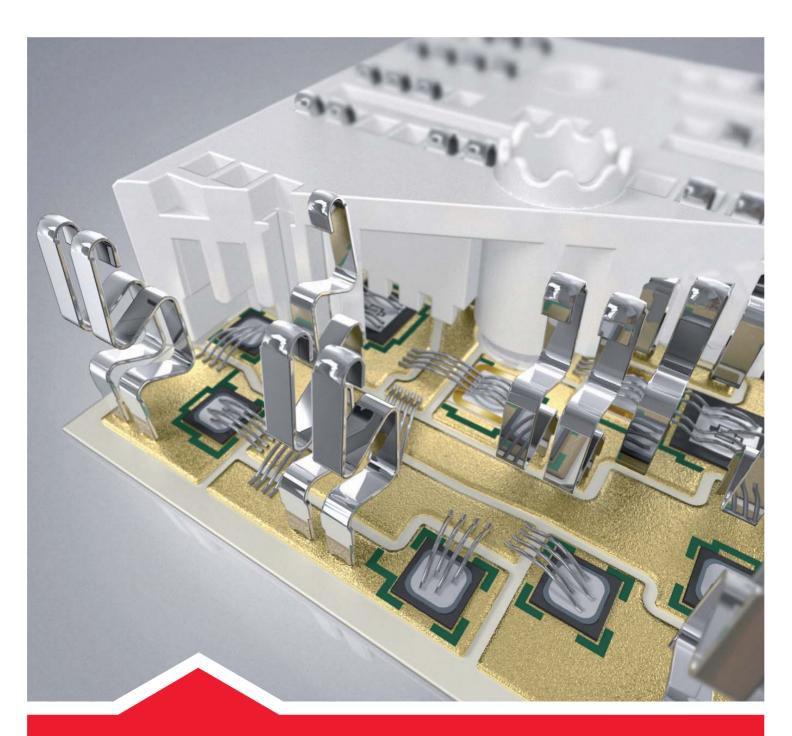

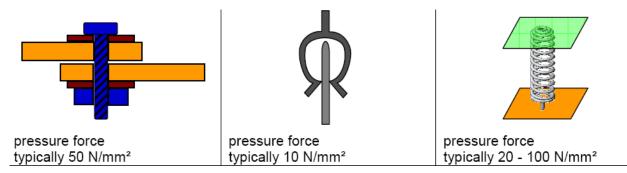

|   |            | Pressure contact                                                    |    |

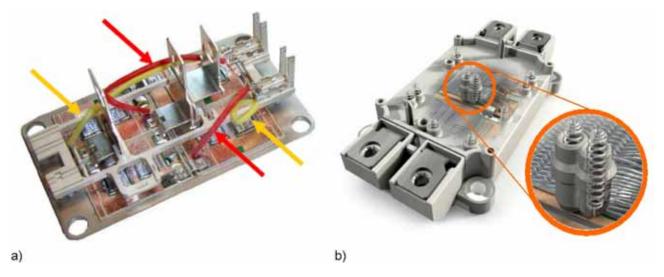

|   | 2.5.1.5    | Assembly and connection technology                                  | 76 |

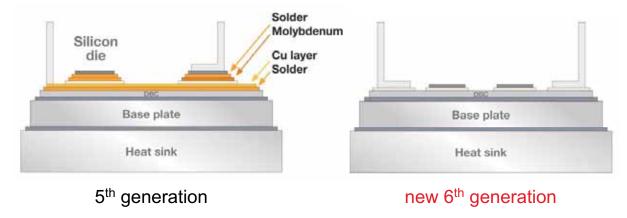

|   |            | Modules with or without base plate                                  |    |

|   |            | nctions and features                                                |    |

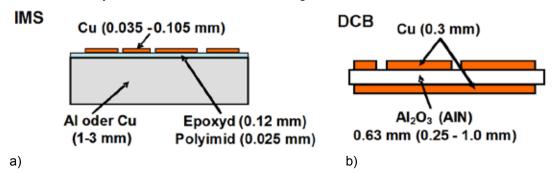

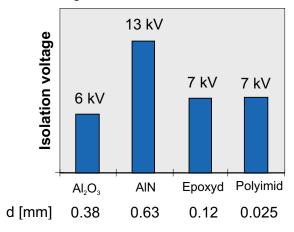

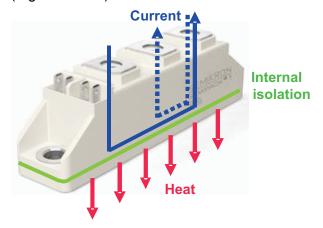

|   |            | Insulation                                                          |    |

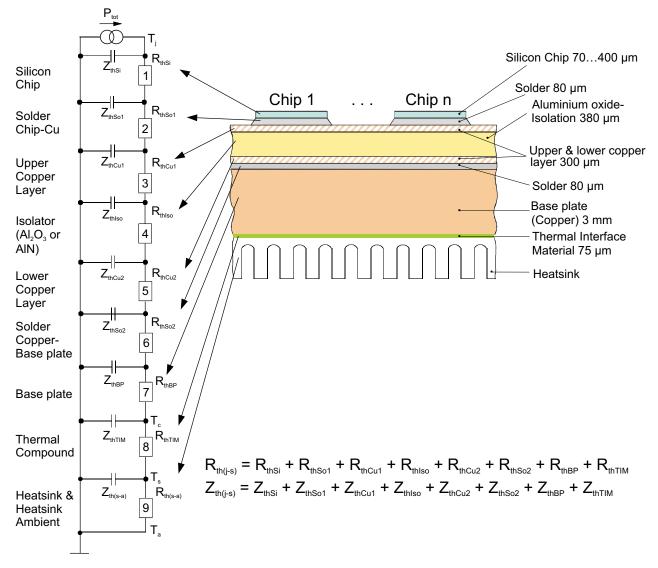

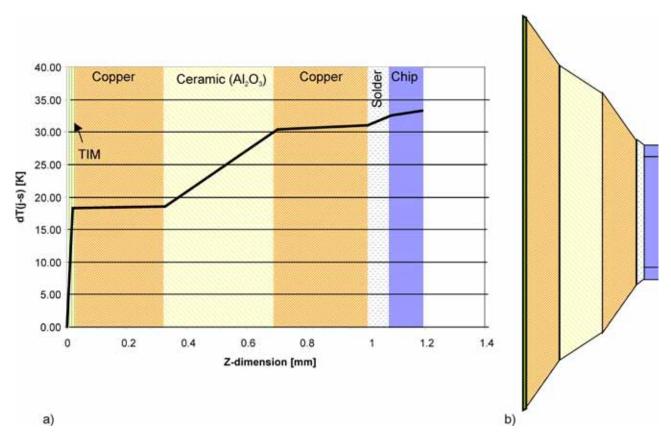

|   |            | Heat dissipation and thermal resistance                             |    |

|   |            | Power cycling capability                                            |    |

|   |            | Current conduction to the main terminals                            |    |

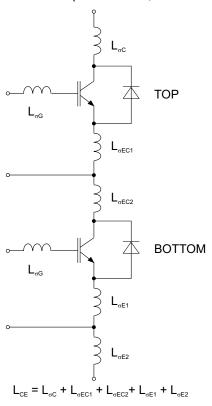

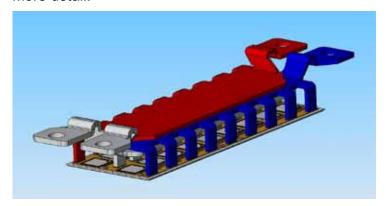

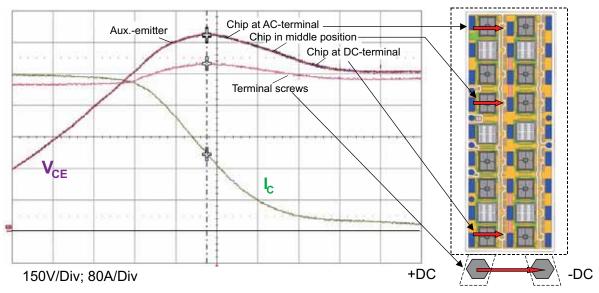

|   |            | Low-inductance internal structure                                   |    |

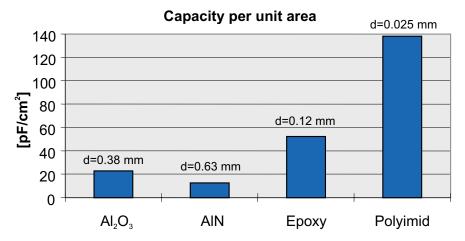

|   |            | Coupling capacitances                                               |    |

|   |            | Circuit complexity                                                  |    |

|   | 2.5.2.8 Defined and safe failure behaviour in the event of module defects    | 96  |

|---|------------------------------------------------------------------------------|-----|

|   | 2.5.2.9 Environmentally compatible recycling                                 | 96  |

|   | 2.5.3 Discrete devices                                                       | 97  |

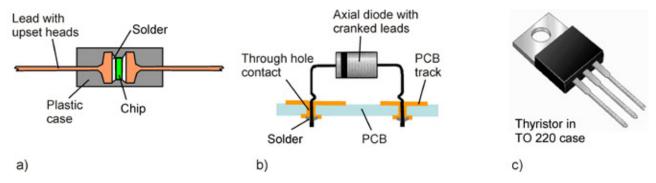

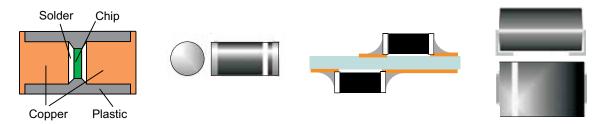

|   | 2.5.3.1 Small rectifiers                                                     | 97  |

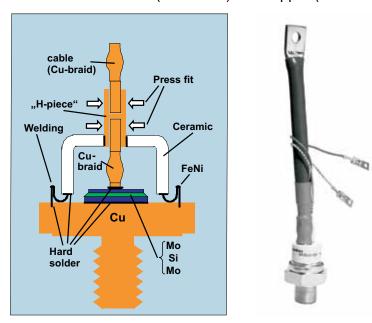

|   | 2.5.3.2 Stud-mounted diodes and stud thyristors                              | 98  |

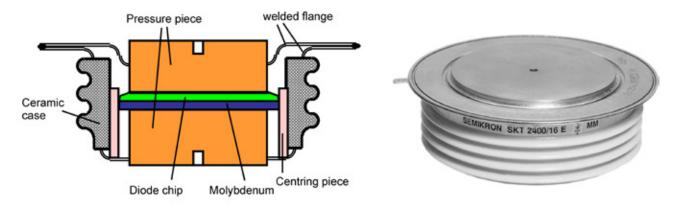

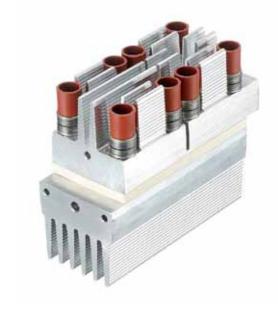

|   | 2.5.3.3 Disk cells                                                           |     |

|   | 2.5.3.4 SEMiSTART®                                                           |     |

|   | 2.5.4 Power modules                                                          |     |

|   | 2.5.4.1 Basics                                                               |     |

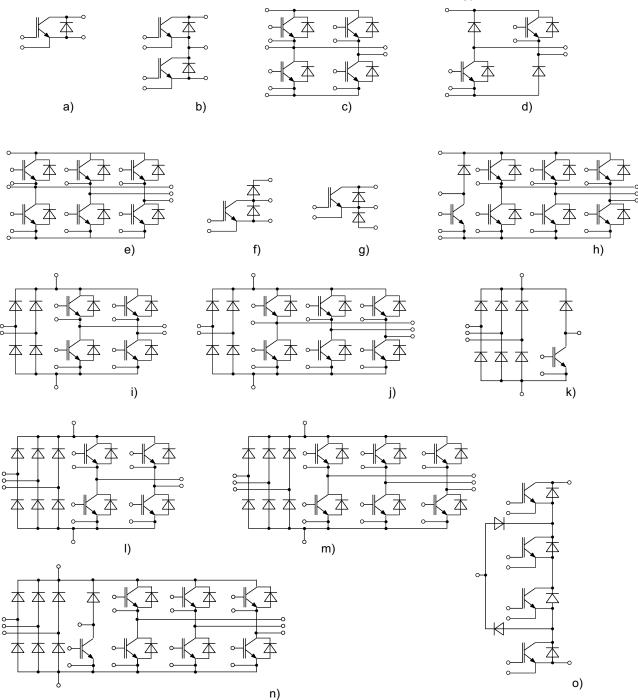

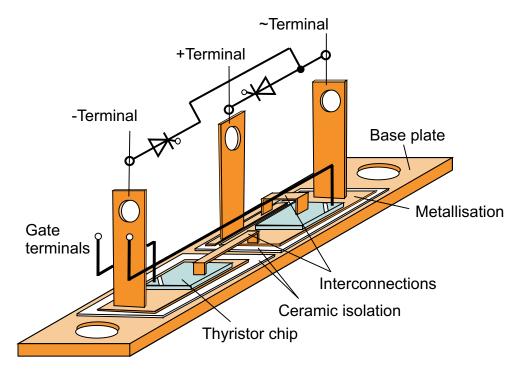

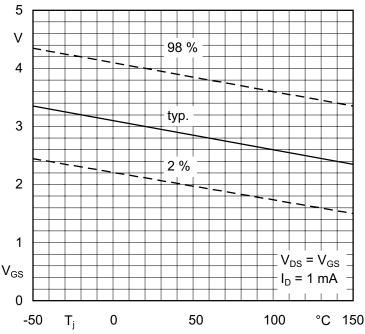

|   | 2.5.4.2 Module families with rectifier diodes and thyristors                 |     |

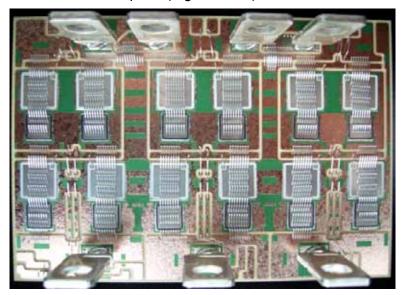

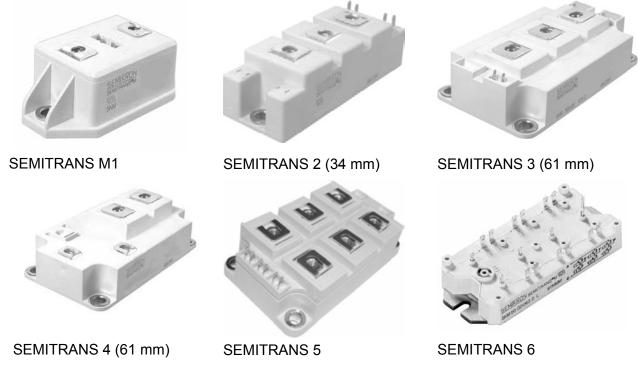

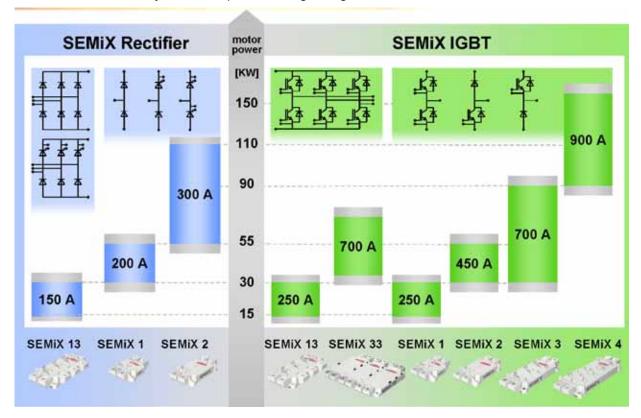

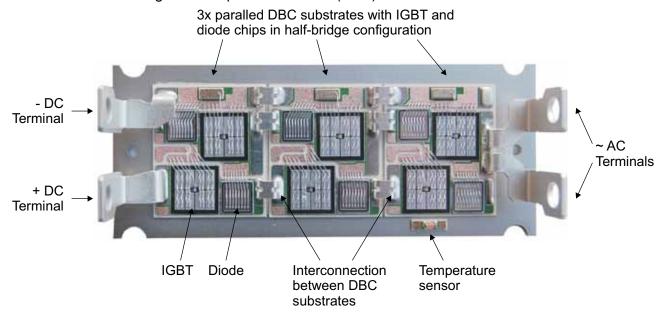

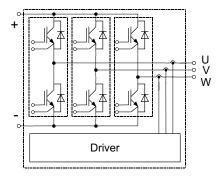

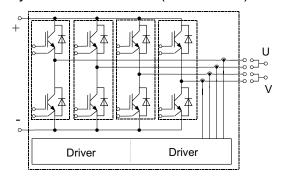

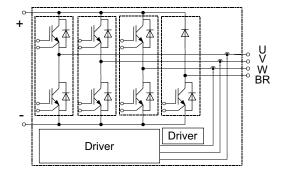

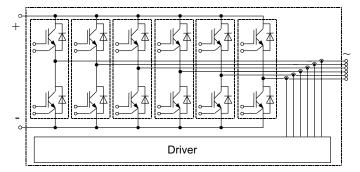

|   | 2.5.4.3 Module families with IGBT and freewheeling diodes                    |     |

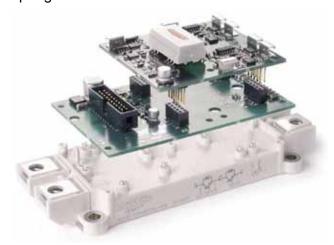

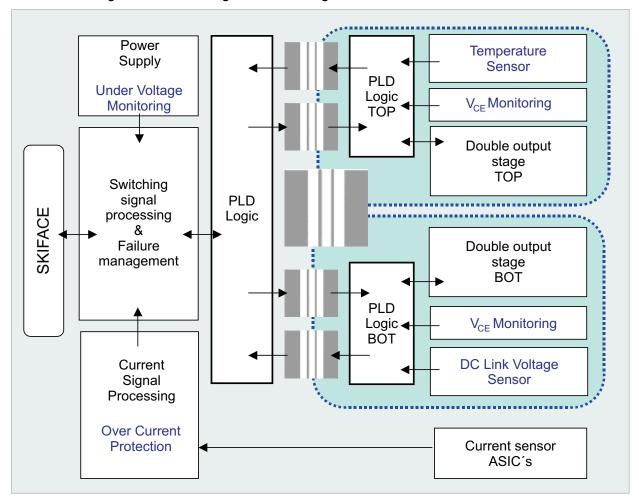

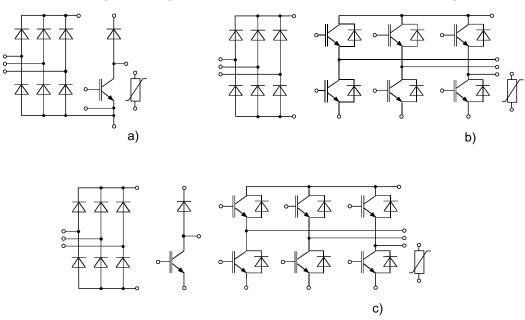

|   | 2.6 Integration of sensors, protective equipment and                         | 104 |

|   | driver electronics                                                           | 110 |

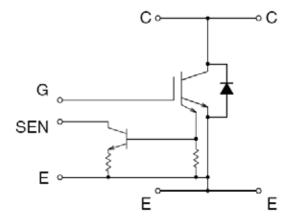

|   | 2.6.1 Modules with integrated current measurement                            |     |

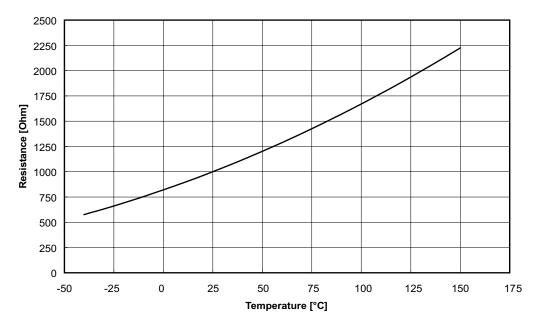

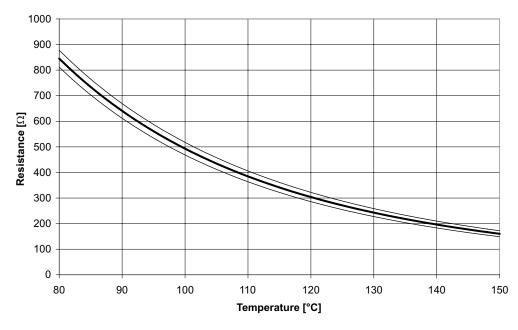

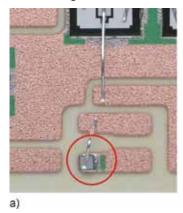

|   | 2.6.2 Modules with integrated temperature measurement                        | 111 |

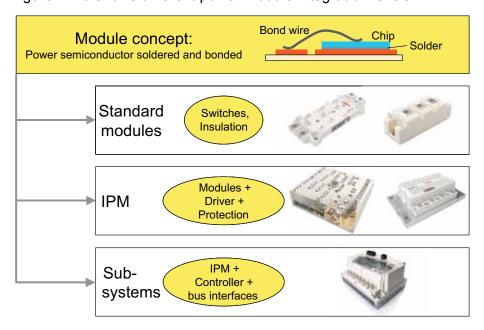

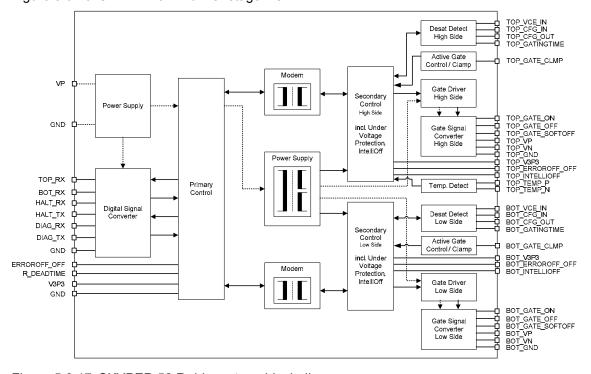

|   | 2.6.3 IPM (Intelligent Power Module)                                         |     |

|   | 2.7 Reliability                                                              |     |

|   | 2.7 Reliability 2.7.1 MTBF, MTTF and FIT rate                                |     |

|   |                                                                              |     |

|   | 2.7.2 Accelerated testing according to Arrhenius                             |     |

|   | 2.7.3 Standard tests for the product qualification and postqualification     |     |

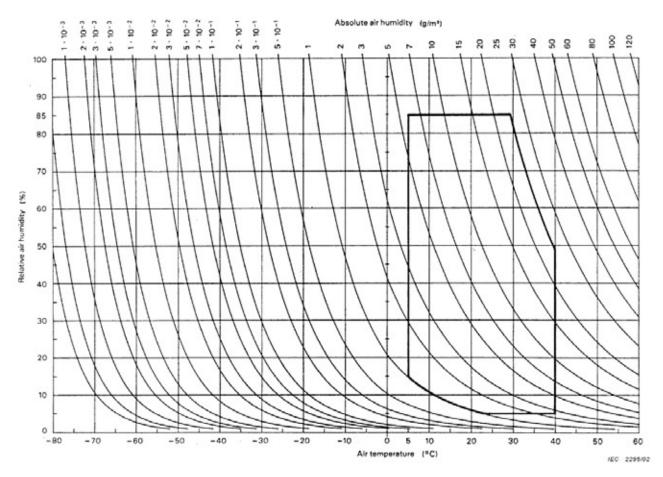

|   | 2.7.3.1 High Temperature Reverse Bias Test (HTRB), High Temperature Gate Bia |     |

|   | Test (HTGB), High Humidity High Temperature Reverse Bias Test (THB)          |     |

|   | 2.7.3.2 High and low temperature storage (HTS, LTS)                          |     |

|   | 2.7.3.3 Temperature cycling test (TC)                                        |     |

|   | 2.7.3.4 Power cycling test (PC)                                              |     |

|   | 2.7.3.5 Vibration test                                                       |     |

|   | 2.7.4 Additional tests for spring contacts                                   |     |

|   | 2.7.4.1 Micro-vibration (fretting corrosion)                                 |     |

|   | 2.7.4.2 Corrosive atmosphere (pollution gas test)                            |     |

|   | 2.7.4.3 Contact-to-PCB temperature cycling                                   |     |

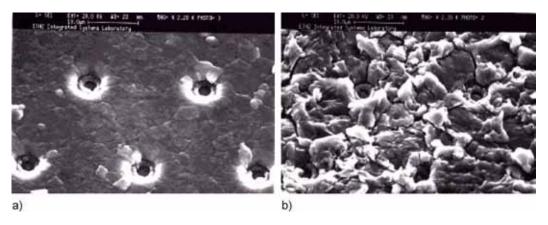

|   | 2.7.5 Failure mechanisms during power cycling                                |     |

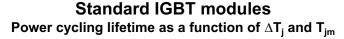

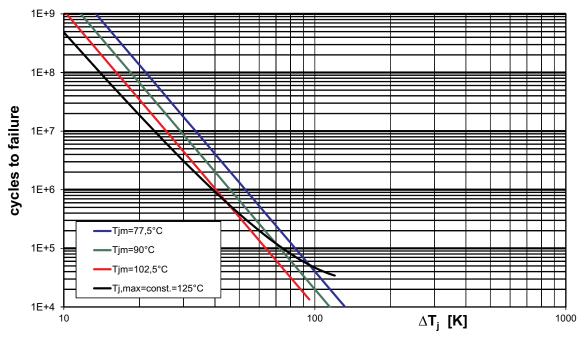

|   | 2.7.6 Evaluation of temperature changes regarding module lifetime            | 126 |

| 3 | Datasheet Ratings for MOSFET, IGBT, Diodes and Thyristors                    | 131 |

|   |                                                                              | 131 |

|   | 3.1.1 Standards                                                              | 131 |

|   | 3.1.2 Letter symbols and terms                                               | 131 |

|   | 3.1.3 Maximum ratings and characteristics                                    |     |

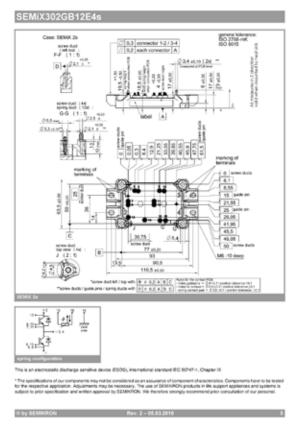

|   | 3.1.4 Component (type) designation system                                    |     |

|   | 3.2 Rectifier diodes and thyristors                                          |     |

|   | 3.2.1 Temperatures                                                           |     |

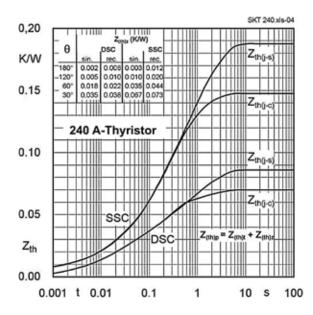

|   | 3.2.2 Thermal impedance and thermal resistance                               |     |

|   | 3.2.3 Mechanical data                                                        |     |

|   | 3.2.4 Rectifier diodes                                                       |     |

|   | 3.2.4.1 Maximum ratings                                                      |     |

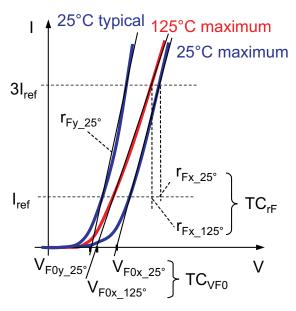

|   | 3.2.4.2 Characteristics                                                      |     |

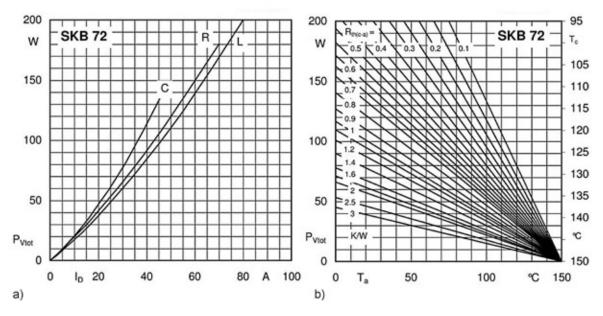

|   | 3.2.4.3 Diagrams                                                             |     |

|   | 3.2.5 Thyristors                                                             |     |

|   | 3.2.5.1 Maximum ratings                                                      |     |

|   | 3.2.5.2 Characteristics                                                      |     |

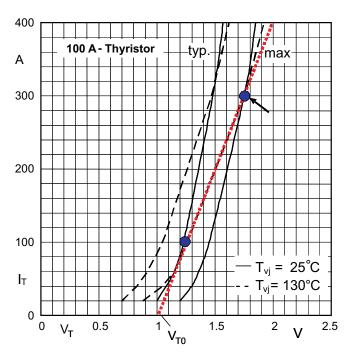

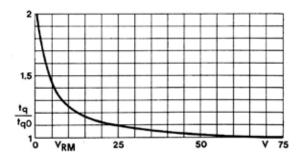

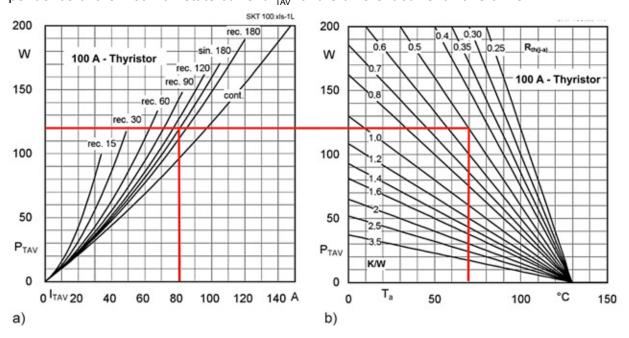

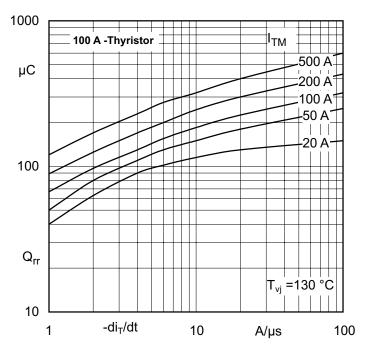

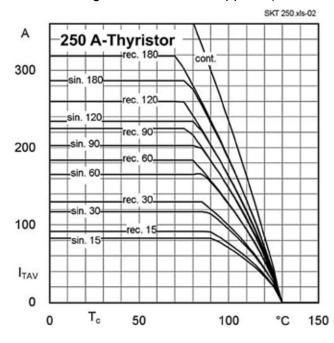

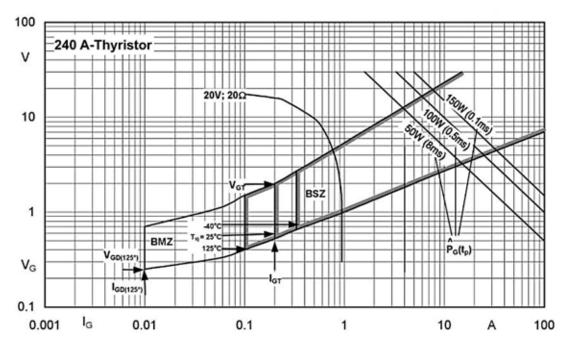

|   | 3.2.5.3 Diagrams                                                             |     |

|   | 3.2.6 Diode and thyristor modules                                            |     |

|   | 3.2.6.1 Maximum ratings and characteristics                                  |     |

|   | 3.2.6.2 Diagrams                                                             |     |

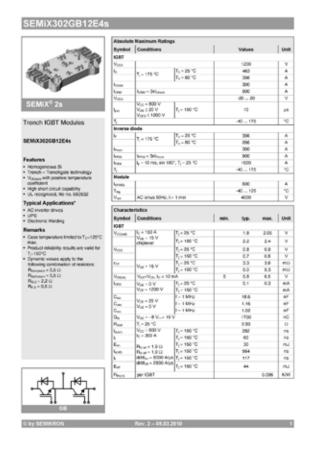

|   | 3.3 IGBT modules                                                             |     |

|   | 3.3.1 Maximum ratings                                                        |     |

|   |                                                                              |     |

|   | 3.3.1.1 IGBT maximum ratings                                                                                                                 | 160                                    |

|---|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 3.3.1.2 Maximum ratings of integrated inverse diodes (freewheeling diodes)                                                                   |                                        |

|   | 3.3.1.3 Maximum module ratings                                                                                                               |                                        |

|   | 3.3.2 Characteristics                                                                                                                        |                                        |

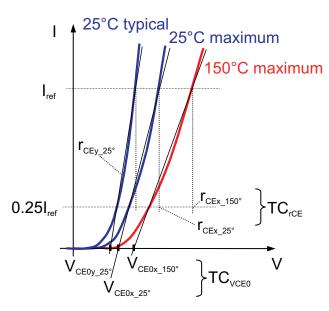

|   | 3.3.2.1 IGBT characteristics                                                                                                                 |                                        |

|   | 3.3.2.2 Characteristics of integrated hybrid inverse diodes (freewheeling diodes).                                                           |                                        |

|   | 3.3.2.3 Module layout characteristics                                                                                                        |                                        |

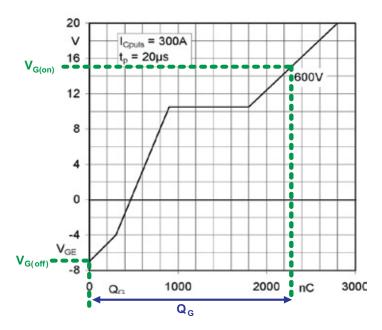

|   | 3.3.3 Diagrams                                                                                                                               |                                        |

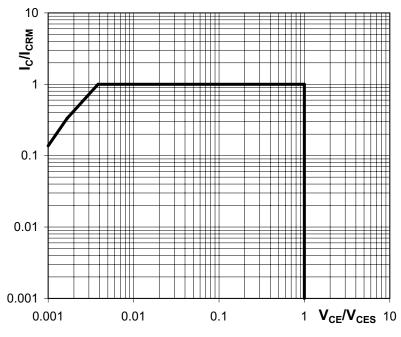

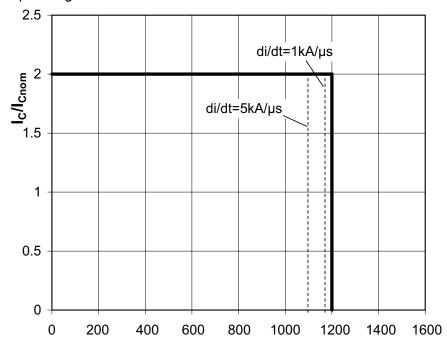

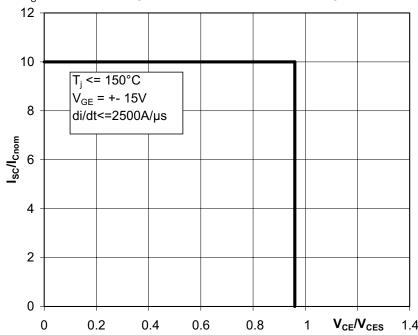

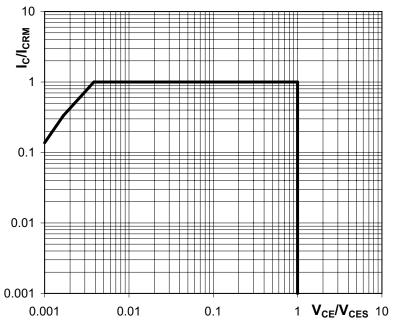

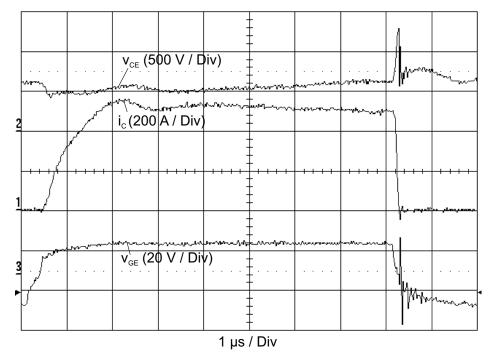

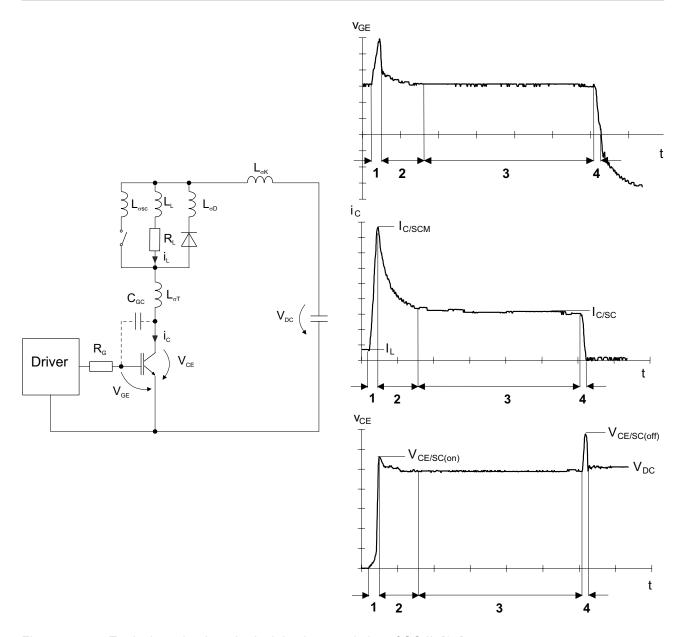

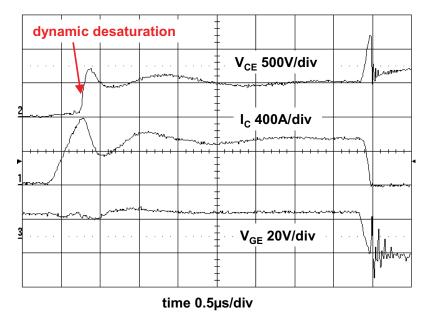

|   | 3.3.4 Safe operating areas during switching operation                                                                                        |                                        |

|   | 3.3.4.1 Maximum safe operating area during single-pulse operation and periodic                                                               | 101                                    |

|   | turn-on (SOA)                                                                                                                                | 101                                    |

|   | <b>\</b>                                                                                                                                     |                                        |

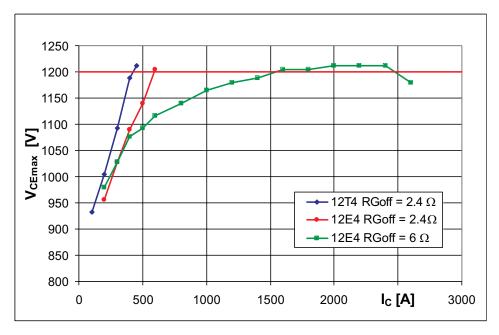

|   | 3.3.4.2 Turn-off safe operating area (RBSOA)                                                                                                 |                                        |

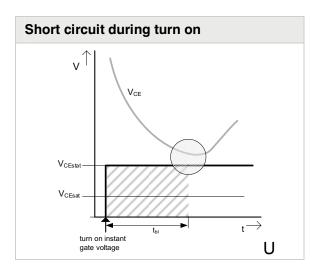

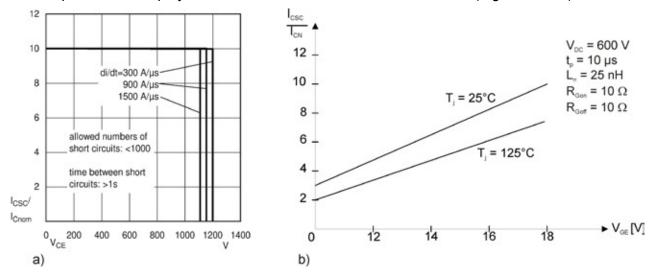

|   | 3.3.4.3 Safe operating area during short circuit                                                                                             |                                        |

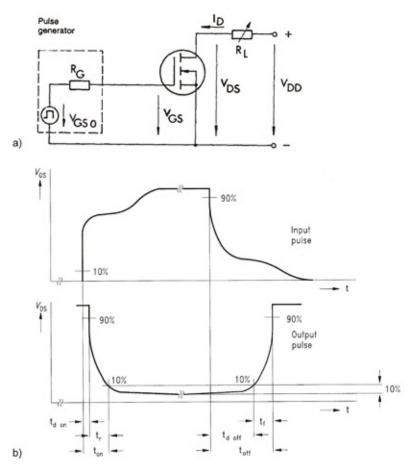

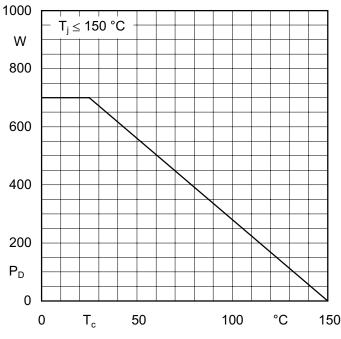

|   | 3.4 Power MOSFET modules                                                                                                                     |                                        |

|   | 3.4.1 Maximum ratings                                                                                                                        |                                        |

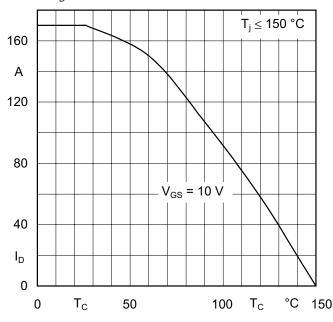

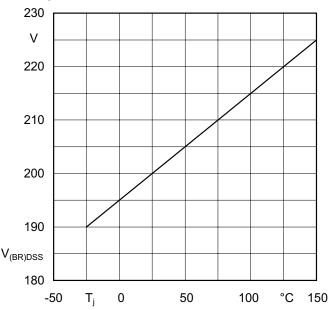

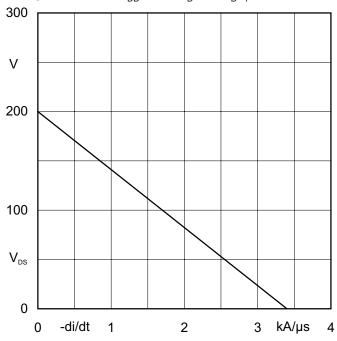

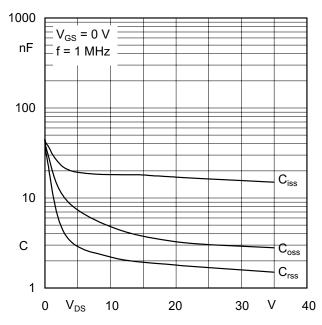

|   | 3.4.1.1 Maximum forward ratings of power MOSFET                                                                                              |                                        |

|   | 3.4.1.2 Maximum ratings of the inverse diodes (power MOSFET ratings in reverse                                                               |                                        |

|   | direction)                                                                                                                                   |                                        |

|   | 3.4.1.3 Maximum module ratings                                                                                                               |                                        |

|   | 3.4.2 Characteristics                                                                                                                        |                                        |

|   | 3.4.2.1 Power MOSFET characteristics                                                                                                         |                                        |

|   | 3.4.2.2 Characteristics of inverse diodes (power MOSFET in reverse direction)                                                                |                                        |

|   | 3.4.2.3 Mechanical module data                                                                                                               |                                        |

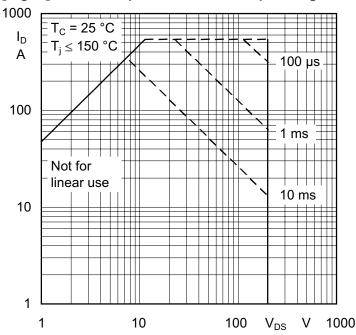

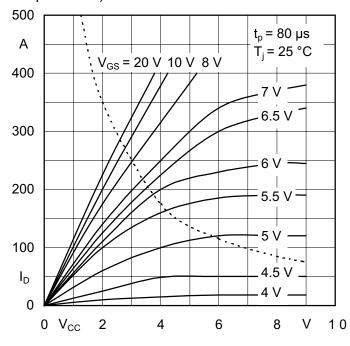

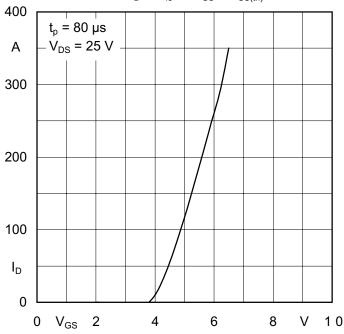

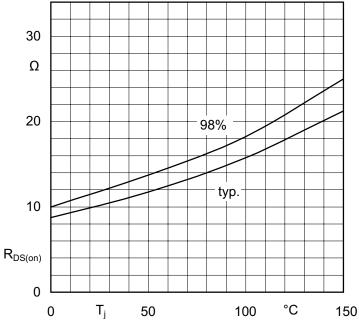

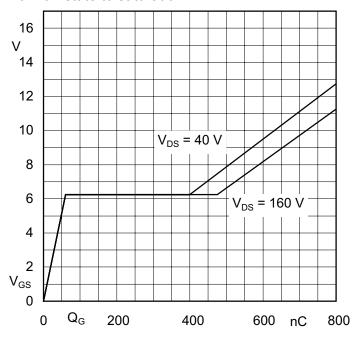

|   | 3.4.3 Diagrams                                                                                                                               |                                        |

|   | 3.5 Supplementary information on CI, CB and CIB power modules                                                                                |                                        |

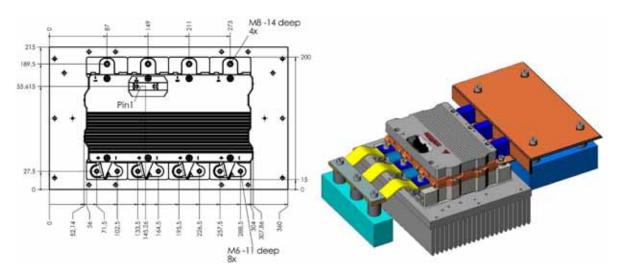

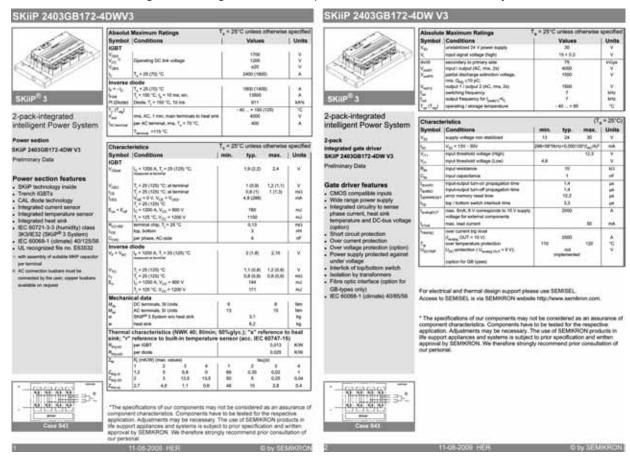

|   | 3.6 Supplementary information on IPMs                                                                                                        |                                        |

|   | 3.6.1 Maximum ratings of the power section                                                                                                   |                                        |

|   | 3.6.2 Maximum ratings of a SKiiP driver                                                                                                      |                                        |

|   | 3.6.3 Characteristics of the SKiiP power section                                                                                             |                                        |

|   | 3.6.4 SKiiP driver characteristics                                                                                                           | 205                                    |

| 4 | Application Notes for Thyristors and Rectifier Diodes                                                                                        | 209                                    |

| = | 4.1 Thyristor and Rectifier Dimensioning and Selection                                                                                       |                                        |

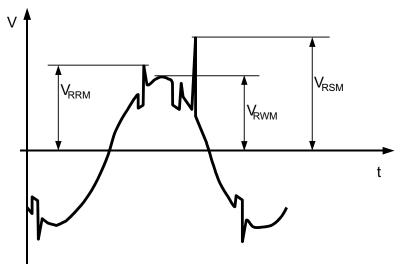

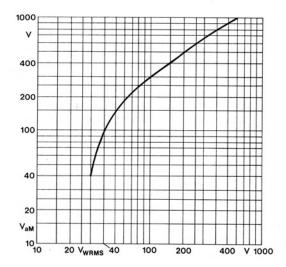

|   | 4.1.1 Reverse voltage                                                                                                                        |                                        |

|   | 4.1.2 Rectifier diodes                                                                                                                       |                                        |

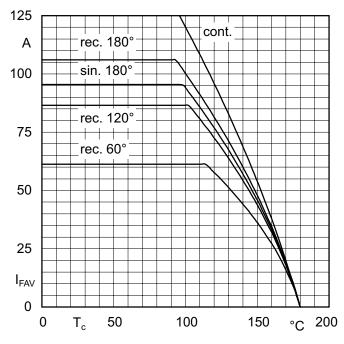

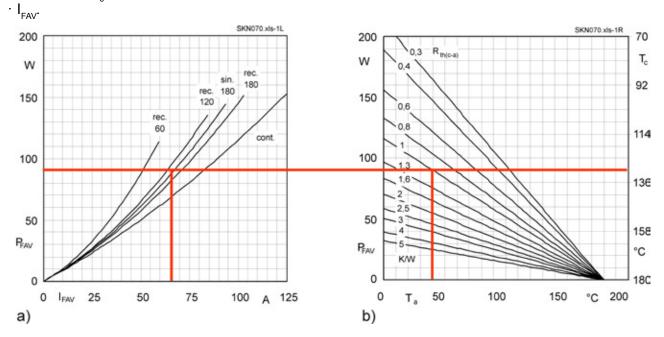

|   | 4.1.2.1 Thermal load in continuous duty                                                                                                      |                                        |

|   | 4.1.2.2 Operation with short-time and intermittent load                                                                                      | 211                                    |

|   | 4.1.2.3 Load at higher frequencies                                                                                                           | 212                                    |

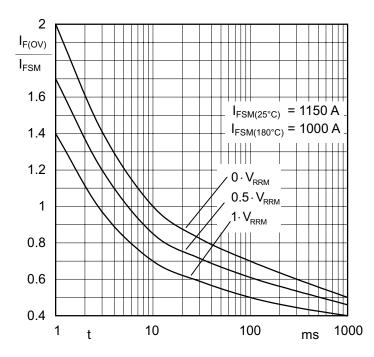

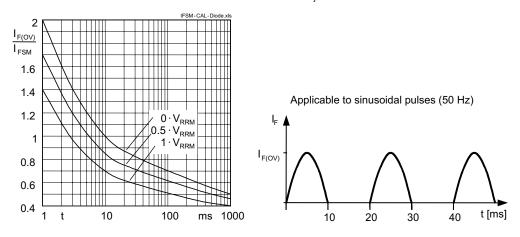

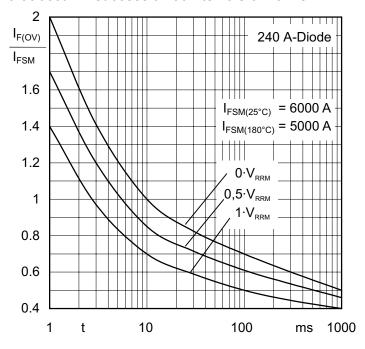

|   | 4.1.2.4 Rated surge forward current for times below and above 10 ms                                                                          |                                        |

|   | 4.1.3 Thyristors                                                                                                                             |                                        |

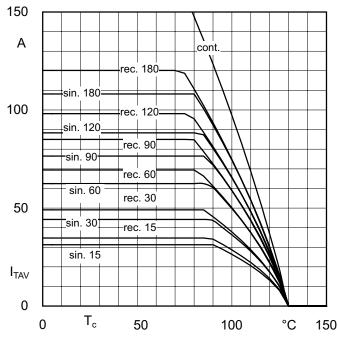

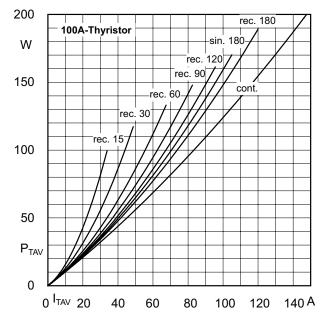

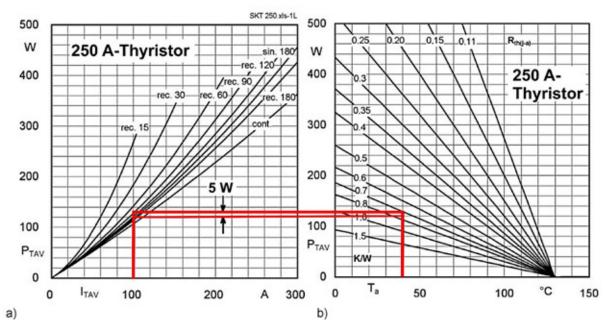

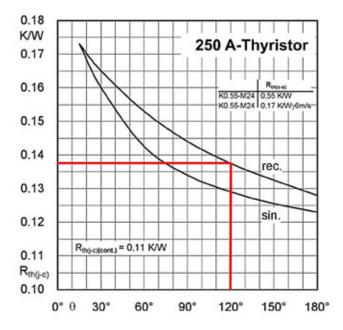

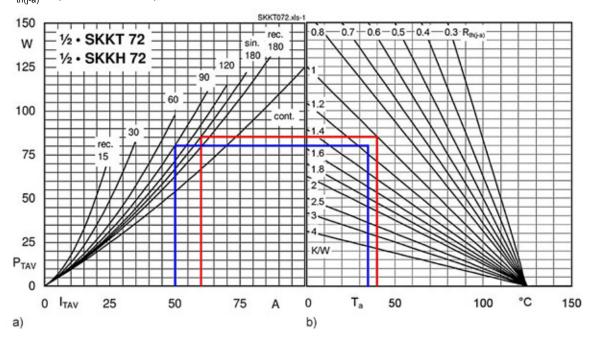

|   | 4.1.3.1 Load in continuous duty                                                                                                              |                                        |

|   | 4.1.3.2 Operation with short-time and intermittent load                                                                                      |                                        |

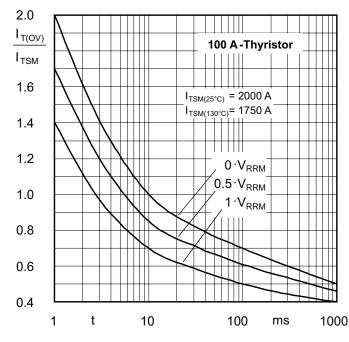

|   | 4.1.3.3 Maximum surge on-state current for times below and above 10 ms                                                                       |                                        |

|   | 4.1.3.4 Critical rate of rise of current and voltage                                                                                         |                                        |

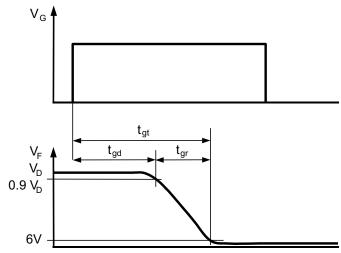

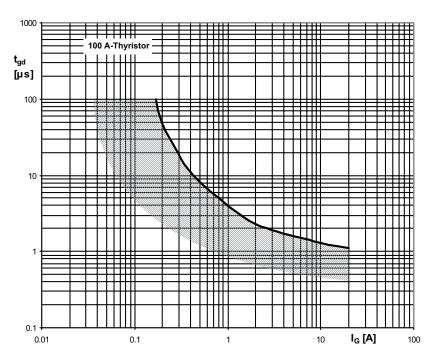

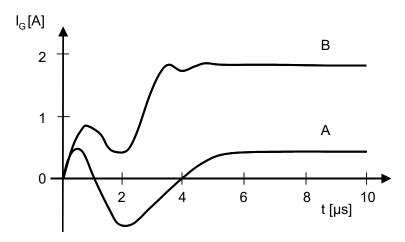

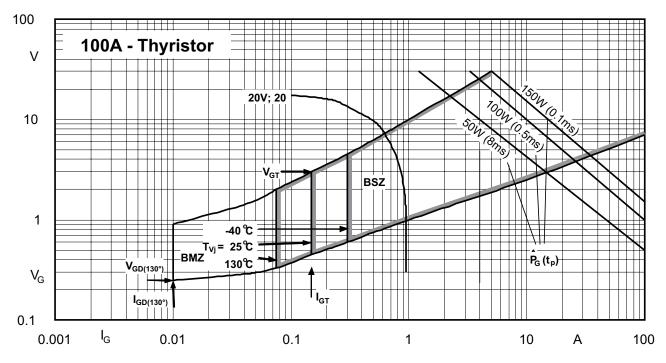

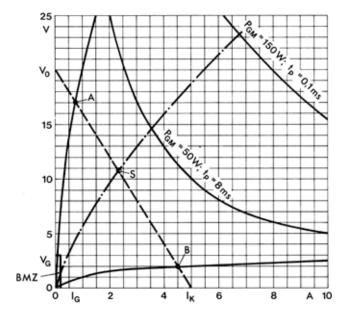

|   | 4.1.3.5 Firing properties                                                                                                                    |                                        |

|   | 4.1.3.5 Filling properties                                                                                                                   |                                        |

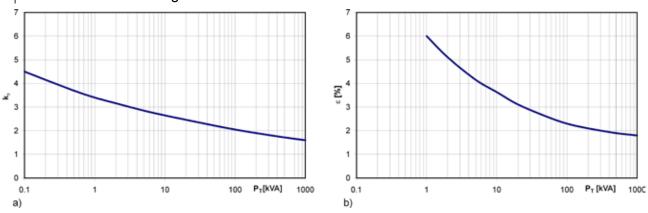

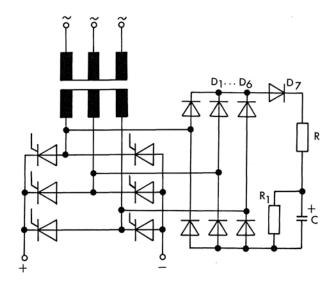

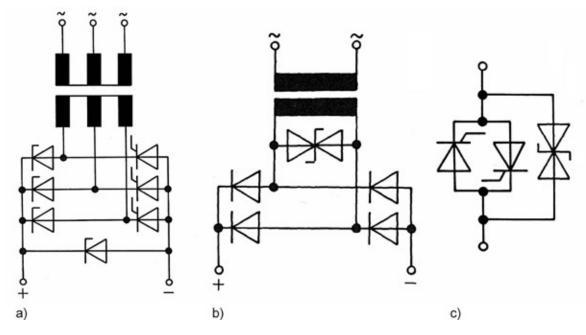

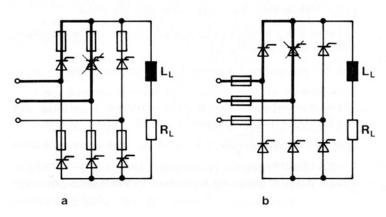

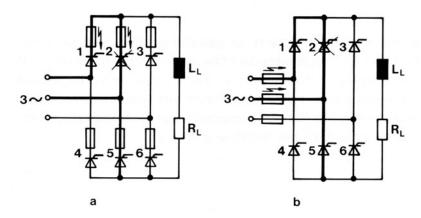

|   | 4.1.5 Bridge Rectifiers                                                                                                                      |                                        |

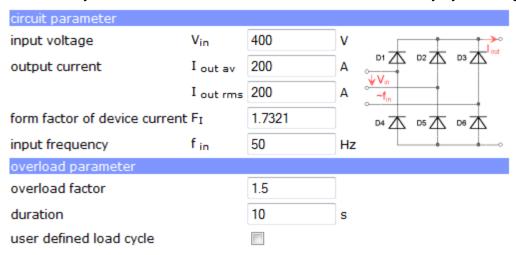

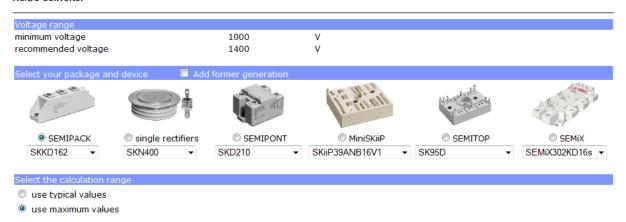

|   | 4.1.6 SemiSel dimensioning software                                                                                                          |                                        |

|   |                                                                                                                                              |                                        |

|   | 1.2 Cooling rectifier components                                                                                                             |                                        |

|   | 4.2 Cooling low-power components                                                                                                             | 222                                    |

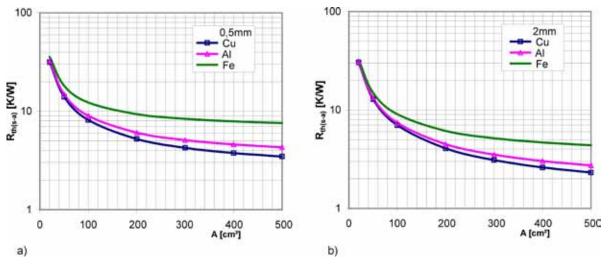

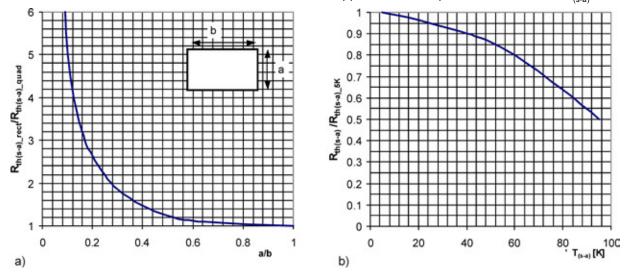

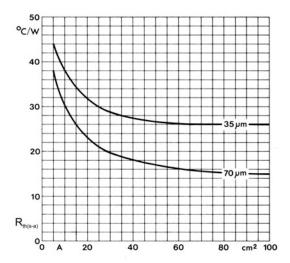

|   | 4.2.1 Cooling low-power components                                                                                                           | 222<br>222                             |

|   | 4.2.1 Cooling low-power components                                                                                                           | 222<br>222<br>222                      |

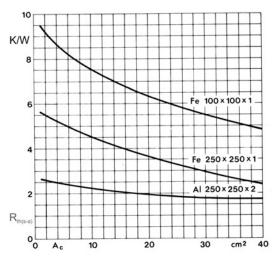

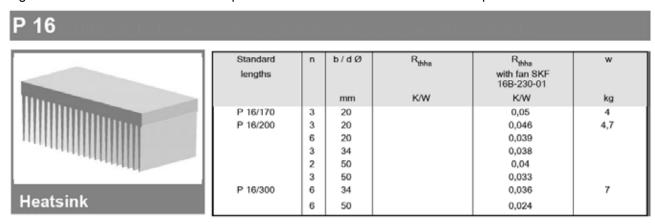

|   | 4.2.1 Cooling low-power components 4.2.2 Cooling plates 4.2.3 Heatsinks                                                                      | 222<br>222<br>222<br>225               |

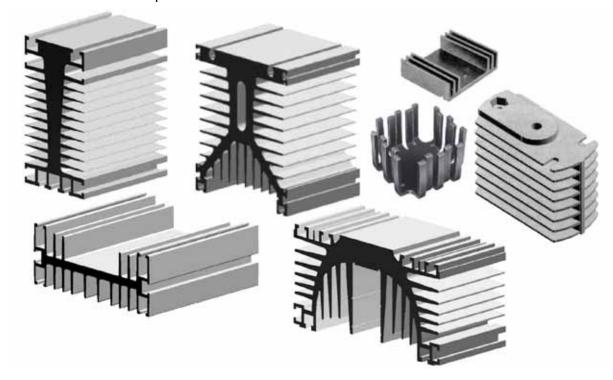

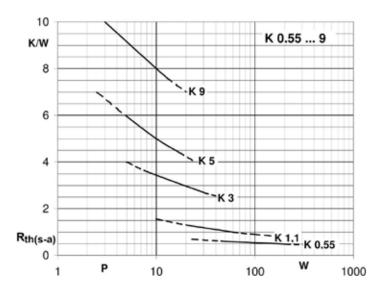

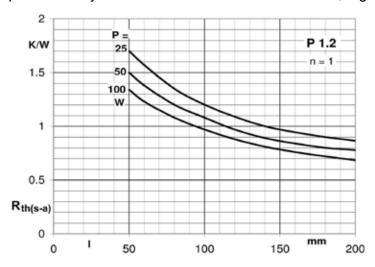

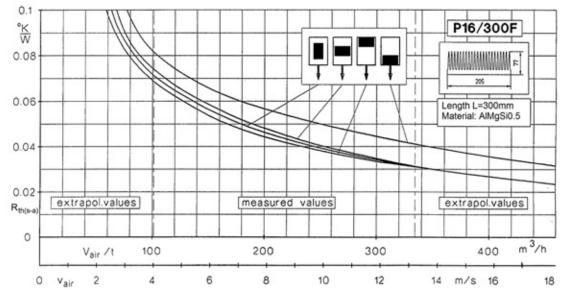

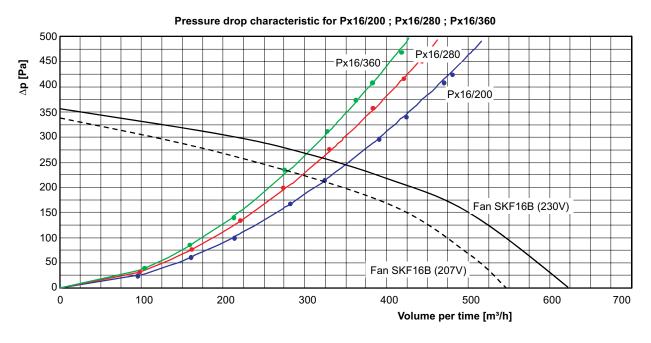

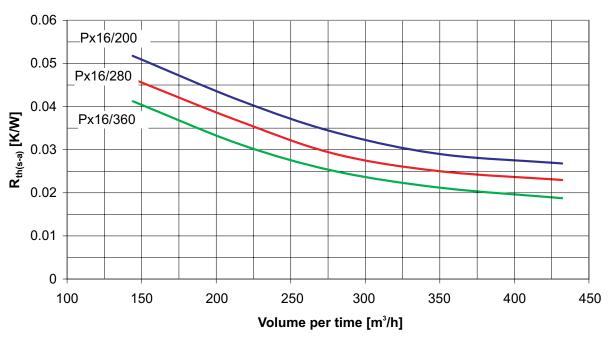

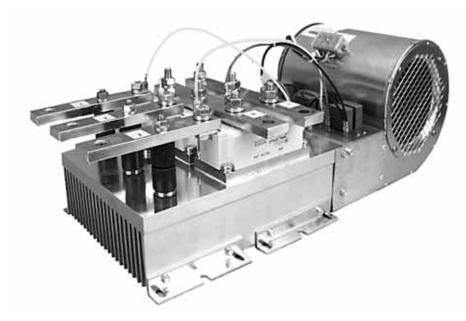

|   | <ul><li>4.2.1 Cooling low-power components</li><li>4.2.2 Cooling plates</li><li>4.2.3 Heatsinks</li><li>4.2.4 Enhanced air cooling</li></ul> | 222<br>222<br>222<br>225<br>227        |

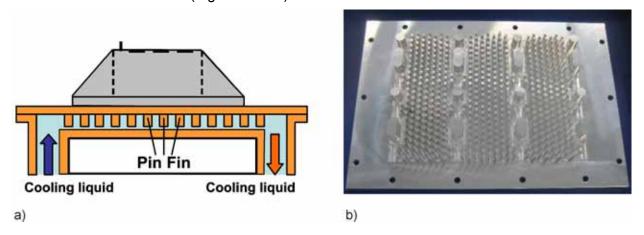

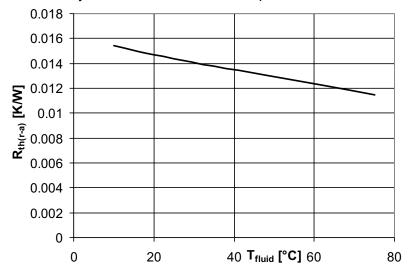

|   | 4.2.1 Cooling low-power components 4.2.2 Cooling plates 4.2.3 Heatsinks                                                                      | 222<br>222<br>222<br>225<br>227<br>230 |

|   | <ul><li>4.2.1 Cooling low-power components</li><li>4.2.2 Cooling plates</li><li>4.2.3 Heatsinks</li><li>4.2.4 Enhanced air cooling</li></ul> | 222<br>222<br>225<br>227<br>230<br>230 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 233                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

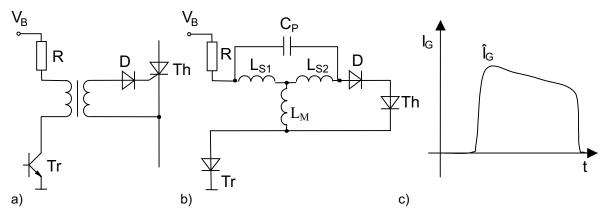

| 4.3.3 Pulse transformers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 233                                                             |

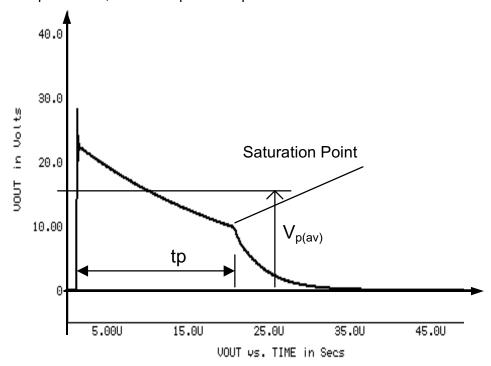

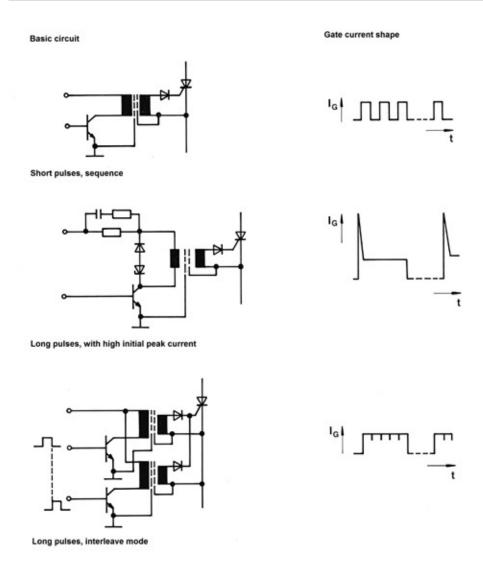

| 4.3.4 Pulse generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 234                                                             |

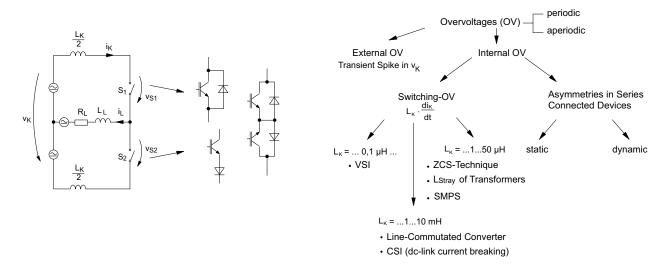

| 4.4 Fault behaviour and diode / thyristor protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                 |

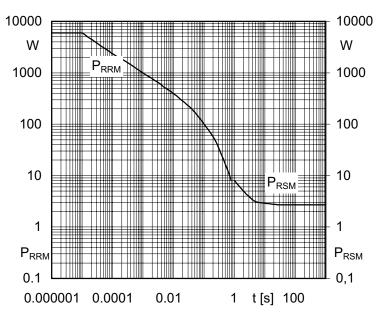

| 4.4.1 General voltage surge protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |

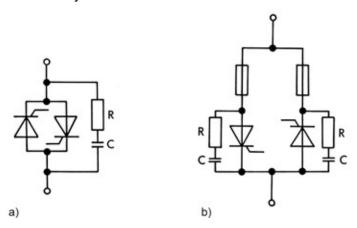

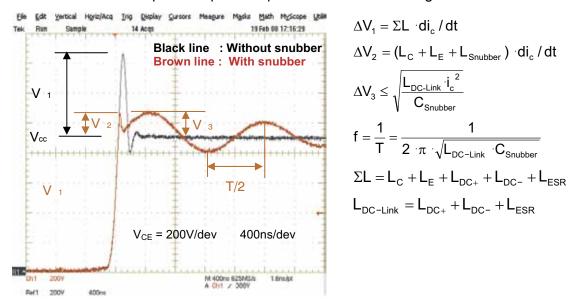

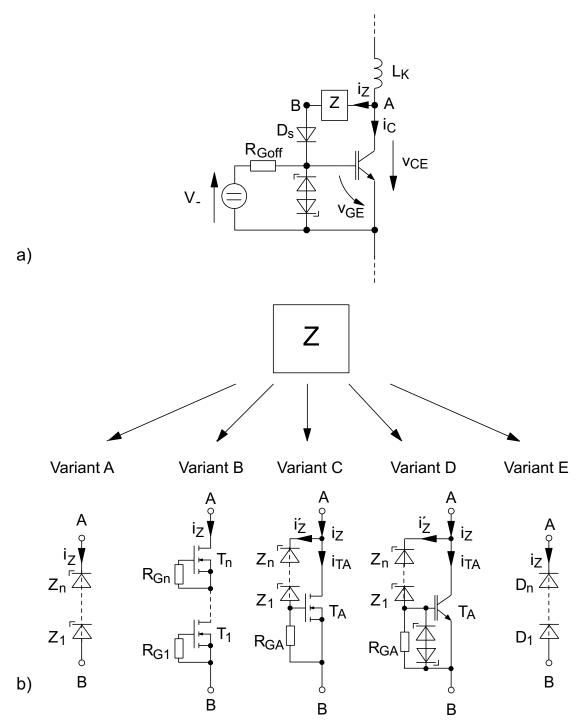

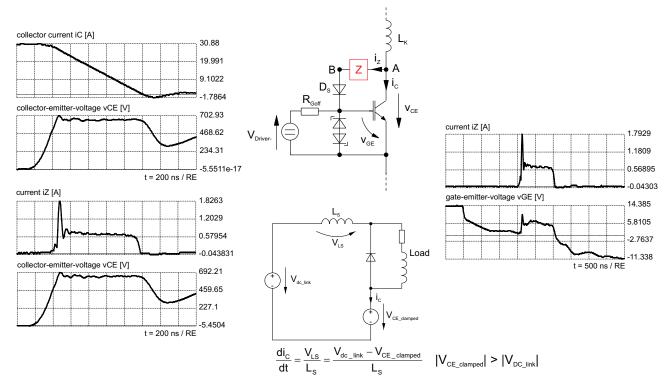

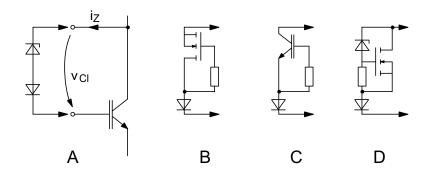

| 4.4.2 Overvoltage protection using resistors and capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 235                                                             |

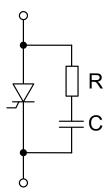

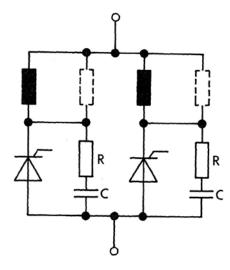

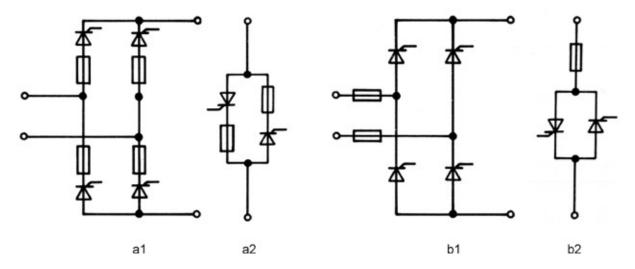

| 4.4.2.1 Snubbers for single switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                 |

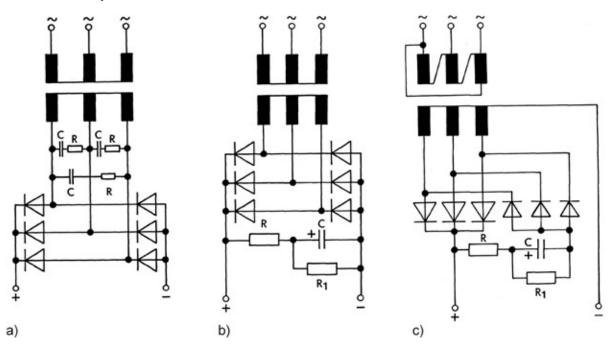

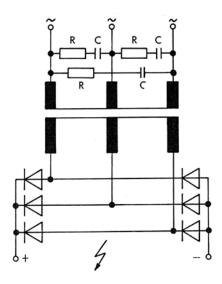

| 4.4.2.2 AC side snubber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                 |

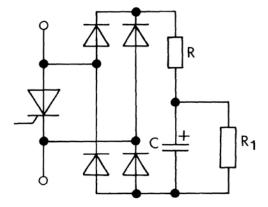

| 4.4.2.3 DC side snubber circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 244                                                             |

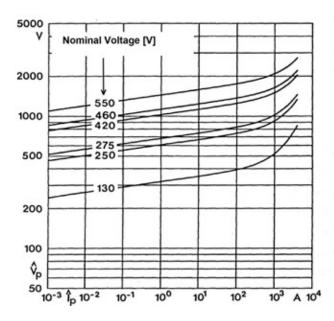

| 4.4.3 Overvoltage protection using varistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 245                                                             |

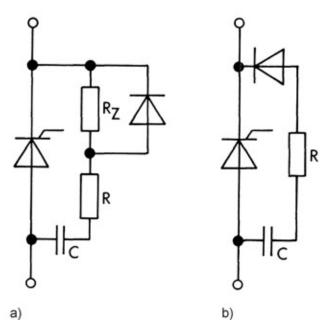

| 4.4.4 Snubber circuits based on silicon avalanche diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 246                                                             |

| 4.4.4.1 Avalanche rectifier diodes featuring self-protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 246                                                             |

| 4.4.4.2 Avalanche diodes as protection for other components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 247                                                             |

| 4.4.4.3 Restrictions in application range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 247                                                             |

| 4.4.4.4 Case types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 248                                                             |

| 4.4.5 Overcurrent protection for diodes and thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |

| 4.4.5.1 Devices for protection from overcurrents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |

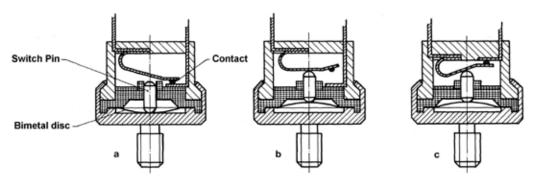

| 4.4.5.2 Protective devices for malfunctions in the cooling device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                 |

| 4.4.5.3 Devices that respond to both overcurrent and cooling unit malfunctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |

| 4.4.6 Short-circuit protection for diodes and thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

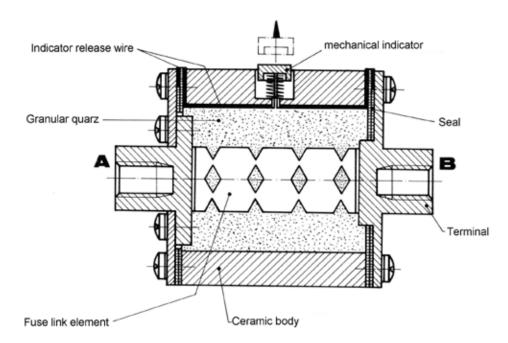

| 4.4.6.1 Semiconductor fuses: terms and explanations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

| 4.4.6.2 Dimensioning semiconductor fuses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

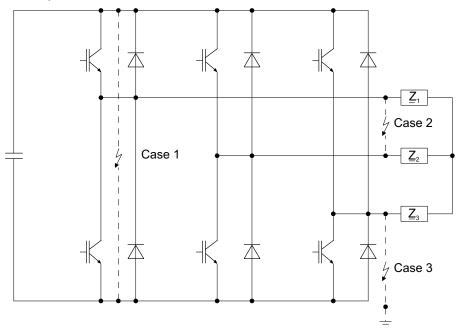

| 4.5 Series and parallel connection of diodes and thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                 |

| 4.5.1 Parallel connection of thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                 |

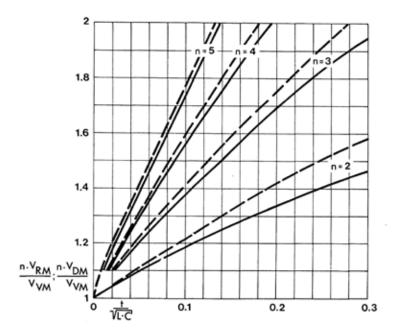

| 4.5.2 Series connection of thyristors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |

| 4.5.3 Parallel connection of rectifier diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |

| 4.5.4 Series connection of rectifier diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

| 5 Application Notes for IGBT and MOSFET Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

| 5.1 Selecting IGBT and MOSFET modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |

| 5.1.1 Operating voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                 |

| 5.1.1.1 Blocking voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |

| 5.1.1.2 Co-ordination of insulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 265                                                             |

| 5.1.2 On-state current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

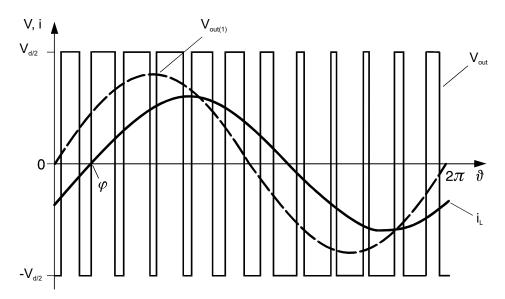

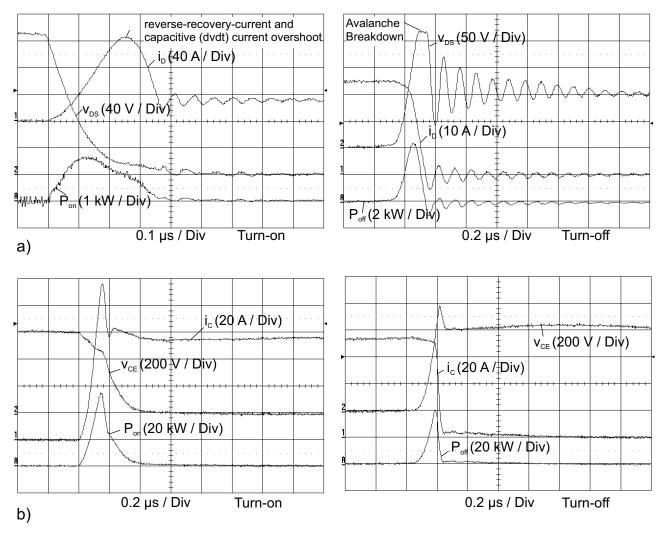

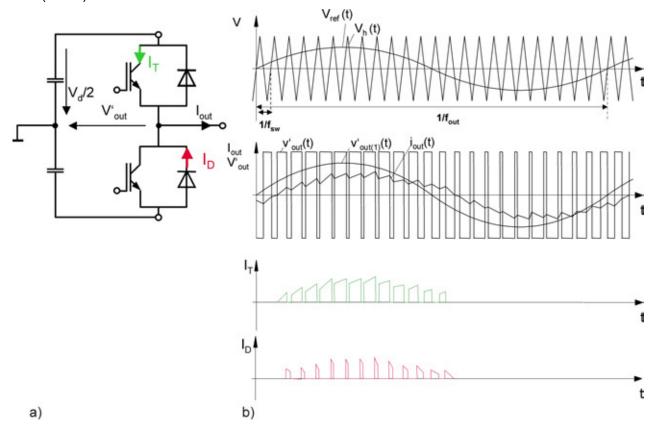

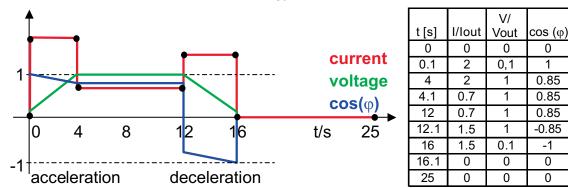

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 269                                                             |

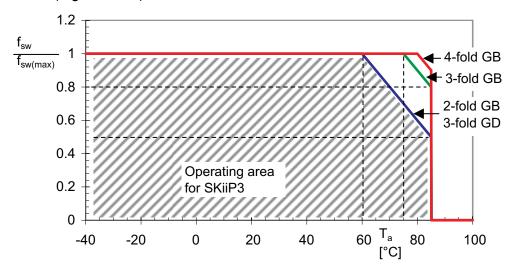

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269<br>271                                                      |

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269<br>271<br>273                                               |

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269<br>271<br>273                                               |

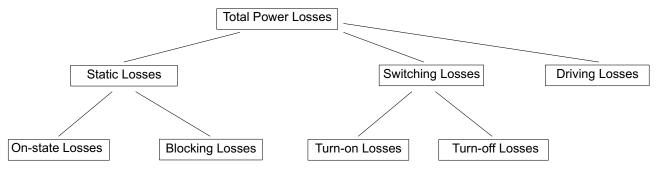

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 269<br>271<br>273<br>274                                        |

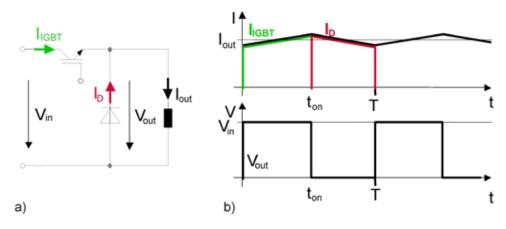

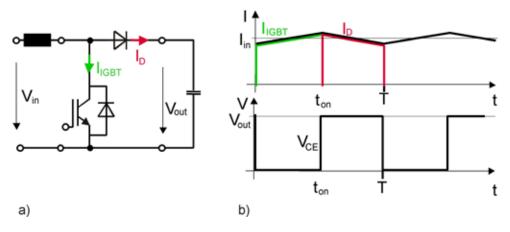

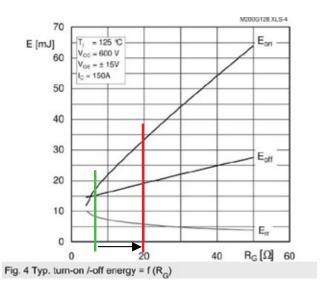

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 269<br>271<br>273<br>274<br>275                                 |

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 269<br>271<br>273<br>274<br>275                                 |

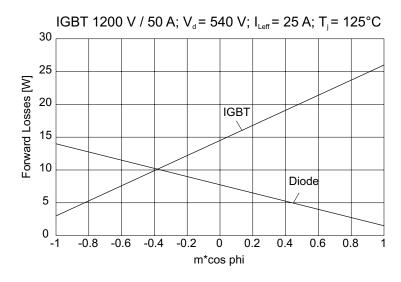

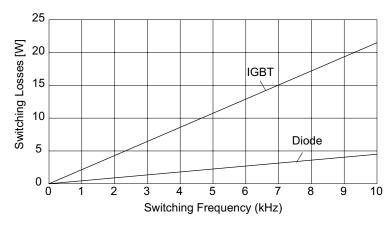

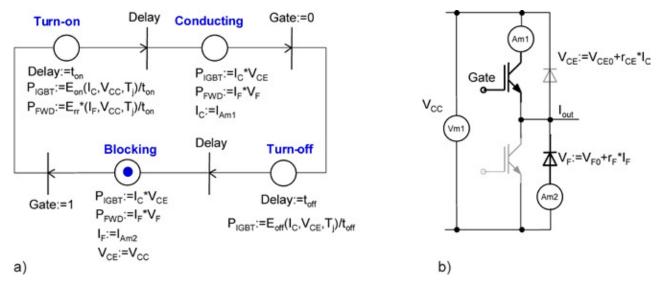

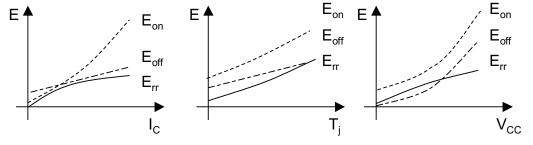

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 269<br>271<br>273<br>274<br>275<br>277                          |

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269<br>271<br>273<br>274<br>275<br>279<br>279                   |

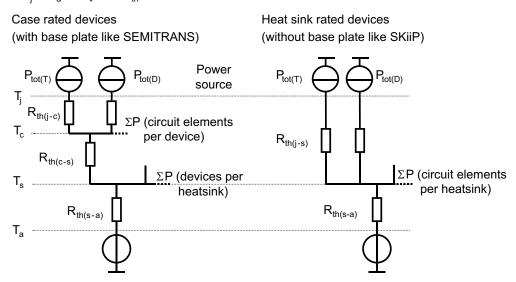

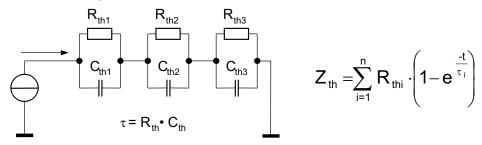

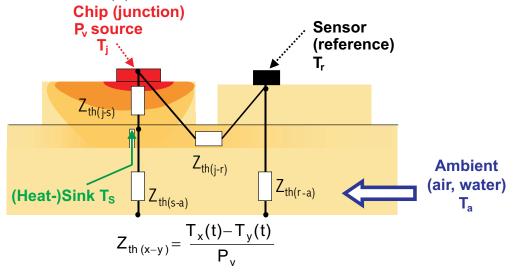

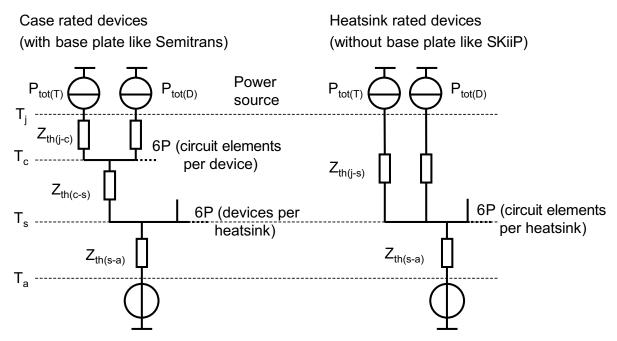

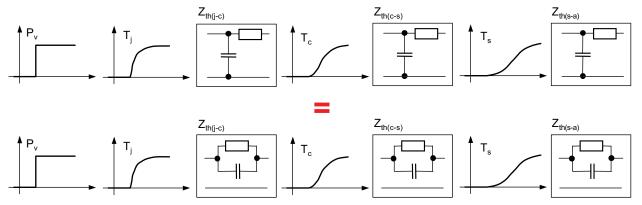

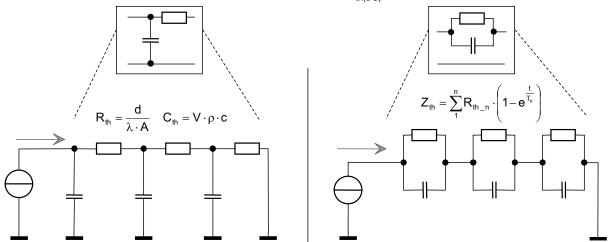

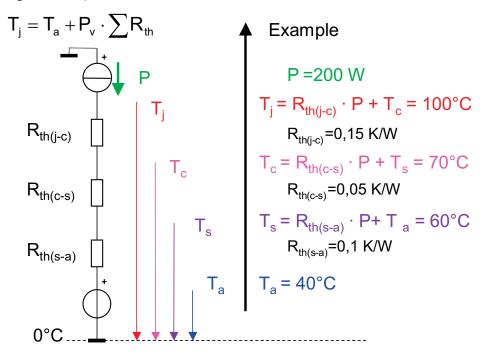

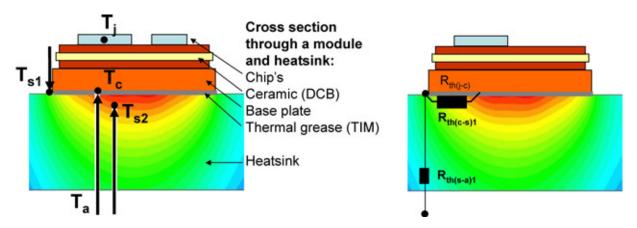

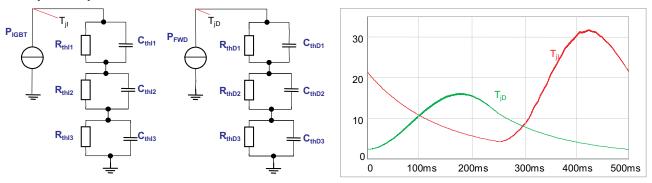

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters 5.2.1.2 PWM voltage inverter 5.2.2 Junction temperature calculation 5.2.2.1 Thermal equivalent circuit diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 269<br>271<br>274<br>275<br>277<br>279<br>279                   |

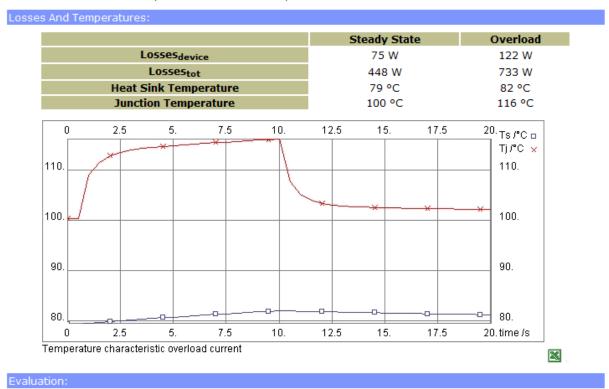

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters 5.2.1.2 PWM voltage inverter 5.2.2 Junction temperature calculation 5.2.2.1 Thermal equivalent circuit diagrams 5.2.2.2 Junction temperature during stationary operation (mean-value analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 269<br>271<br>273<br>274<br>275<br>277<br>279<br>282<br>283     |

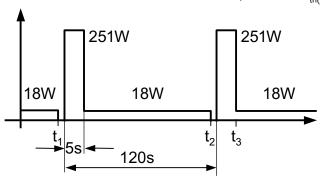

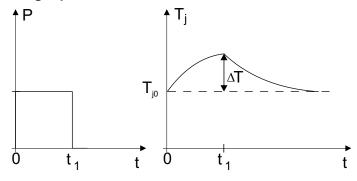

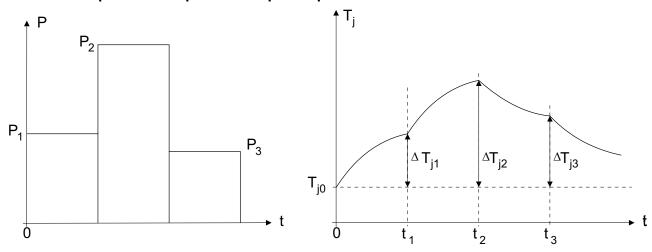

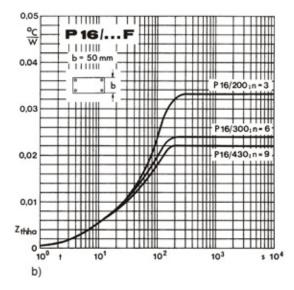

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters 5.2.1.2 PWM voltage inverter 5.2.2 Junction temperature calculation 5.2.2.1 Thermal equivalent circuit diagrams 5.2.2.2 Junction temperature during stationary operation (mean-value analysis 5.2.2.3 Junction temperature during short-time operation                                                                                                                                                                                                                                                                                                                                                                                                                               | 269<br>271<br>273<br>274<br>275<br>279<br>279<br>s) 282<br>283  |

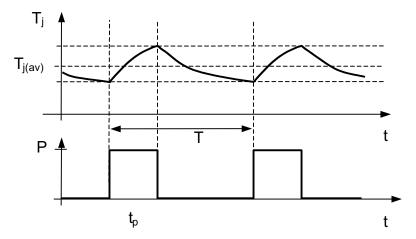

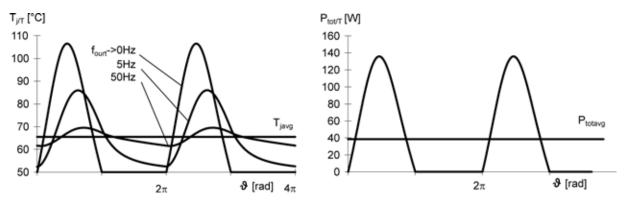

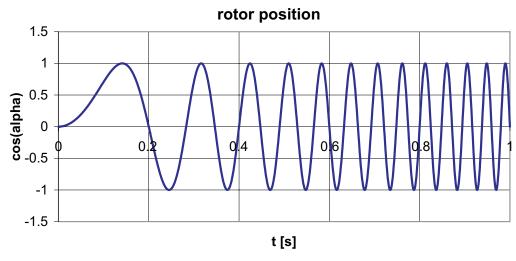

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters 5.2.1.2 PWM voltage inverter 5.2.2 Junction temperature calculation 5.2.2.1 Thermal equivalent circuit diagrams 5.2.2.2 Junction temperature during stationary operation (mean-value analysis 5.2.2.3 Junction temperature during short-time operation 5.2.2.4 Junction temperature at fundamental frequency                                                                                                                                                                                                                                                                                                                                                                         | 269<br>271<br>274<br>275<br>279<br>279<br>282<br>283<br>285     |

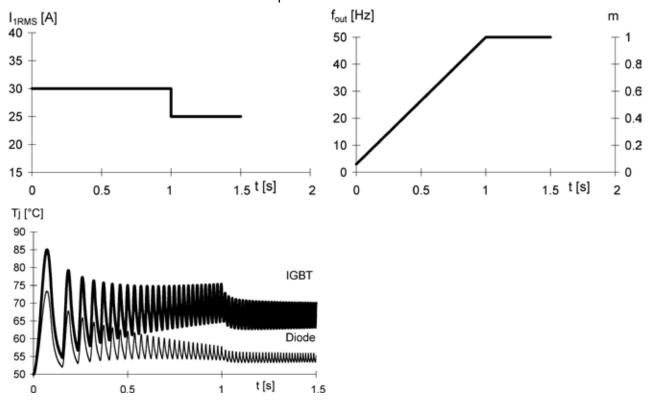

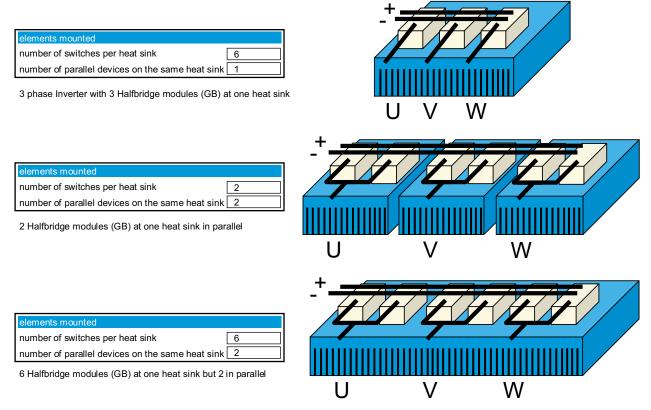

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 269 271 274 275 279 279 282 283 287 287                         |

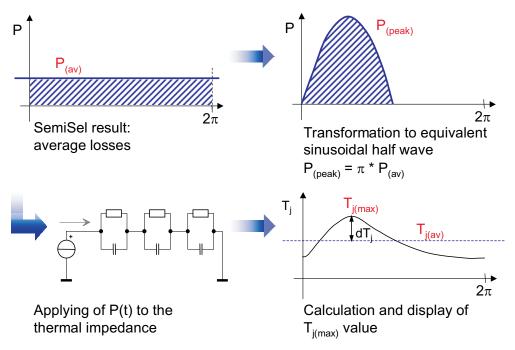

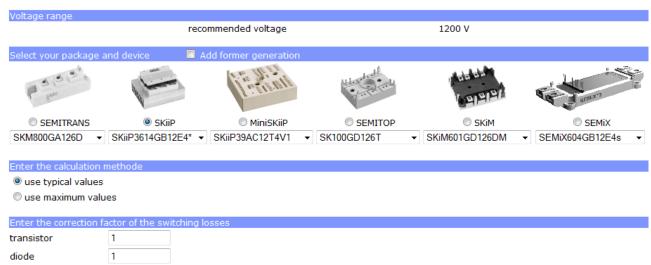

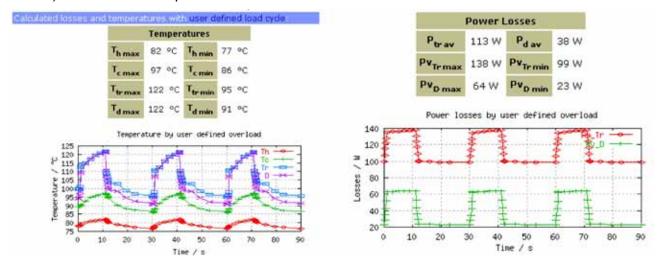

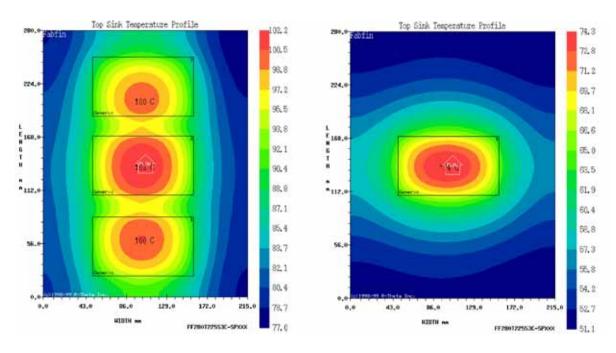

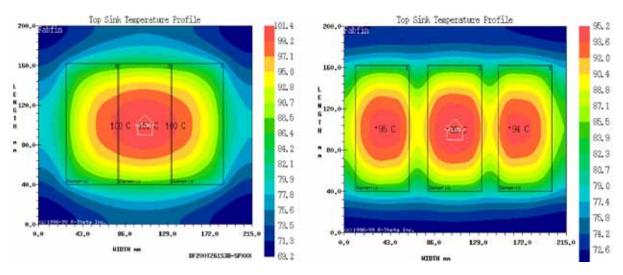

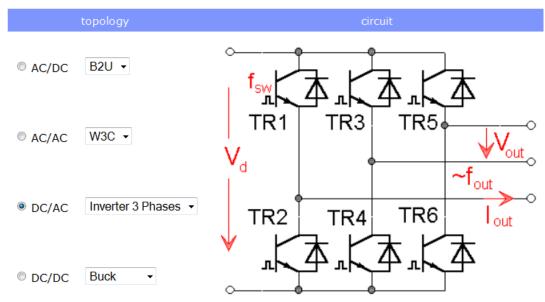

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters 5.2.1.2 PWM voltage inverter 5.2.2 Junction temperature calculation 5.2.2.1 Thermal equivalent circuit diagrams 5.2.2.2 Junction temperature during stationary operation (mean-value analysis 5.2.2.3 Junction temperature during short-time operation 5.2.2.4 Junction temperature at fundamental frequency 5.2.3 Calculation of power dissipation and temperature using SemiSel 5.2.3.1 Possible solution for temperature and power dissipation calculation                                                                                                                                                                                                                        | 269 271 274 275 277 279 282 283 287 287                         |

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269 271 274 275 279 279 282 283 285 287 288                     |

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency 5.2 Thermal dimensioning for power transistor modules 5.2.1 Individual and total losses 5.2.1.1 DC/DC converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 269 271 274 275 279 279 282 283 285 287 287 288                 |

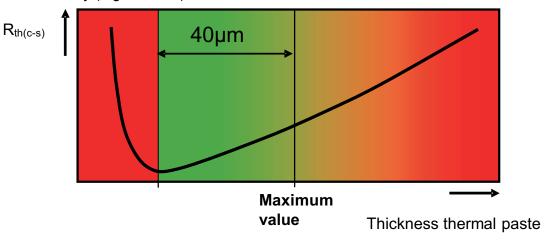

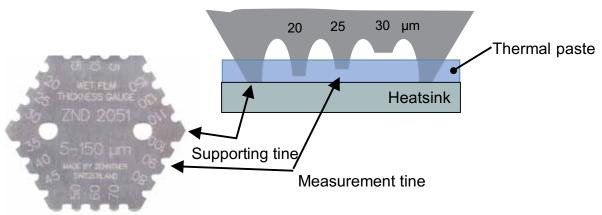

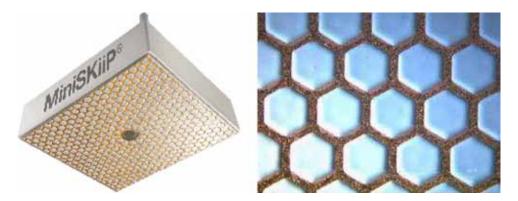

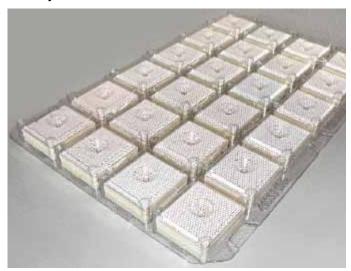

| 5.1.3 Stress conditions of freewheeling diodes in rectifier and inverter mode 5.1.4 Switching frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 269 271 274 275 279 279 282 283 287 287 288 288 289             |